Flexible static memory controller (FSMC) RM0351

430/1830 DocID024597 Rev 5

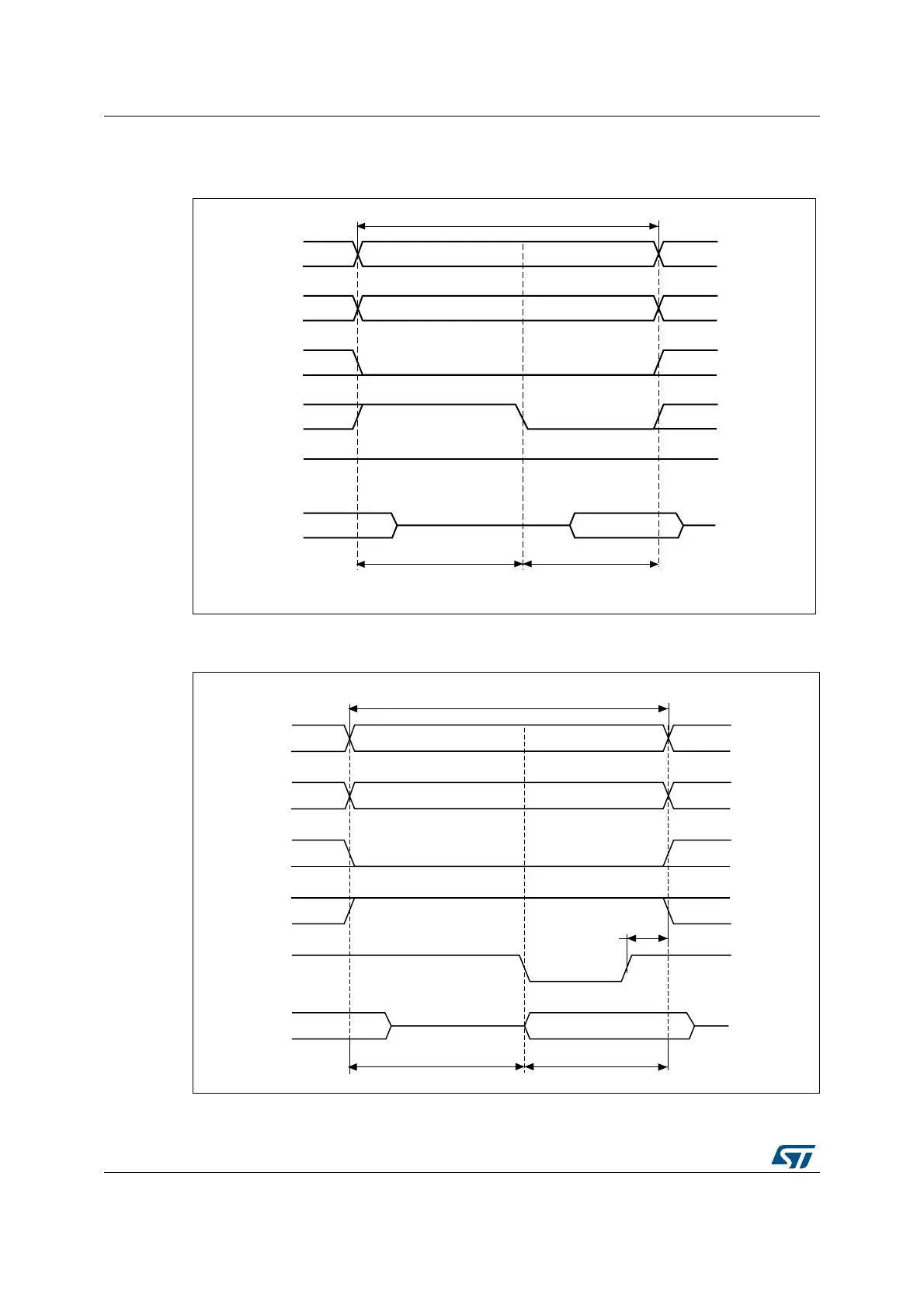

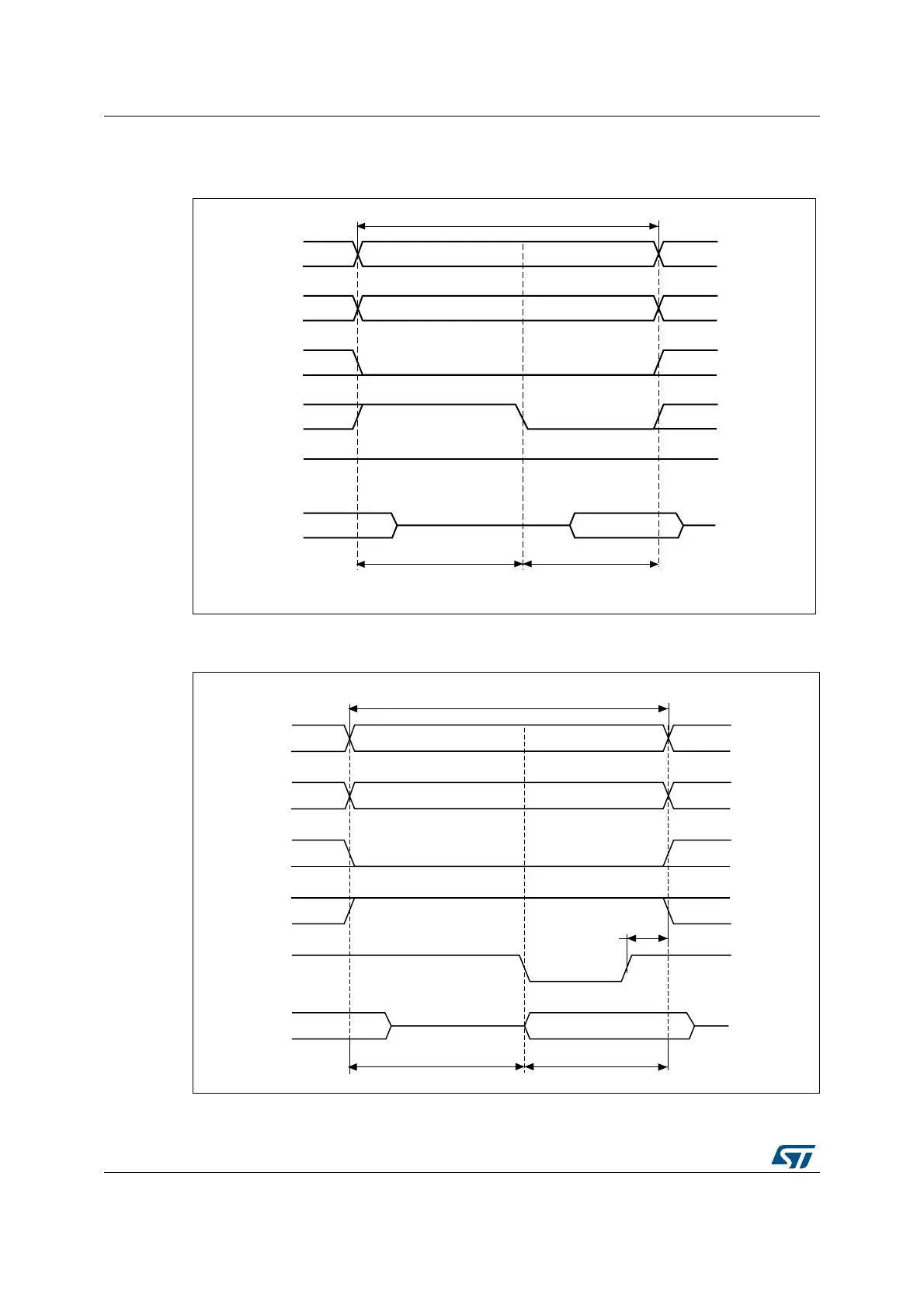

Mode A - SRAM/PSRAM (CRAM) OE toggling

Figure 40. ModeA read access waveforms

1. NBL[1:0] are driven low during the read access

Figure 41. ModeA write access waveforms

!;=

./%

!$$3%4 $!4!34

-EMORYTRANSACTION

.%X

$;=

(#,+CYCLES (#,+CYCLES

.7%

.",;=

DATADRIVEN

BYMEMORY

-36

(IGH

06Y9

$>@

12(

$''6(7 '$7$67

0HPRU\WUDQVDFWLRQ

1([

'>@

+&/.F\FOHV +&/.F\FOHV

1:(

1%/>@

GDWDGULYHQE\)0&

+&/.

Loading...

Loading...