Liquid crystal display controller (LCD) RM0351

764/1830 DocID024597 Rev 5

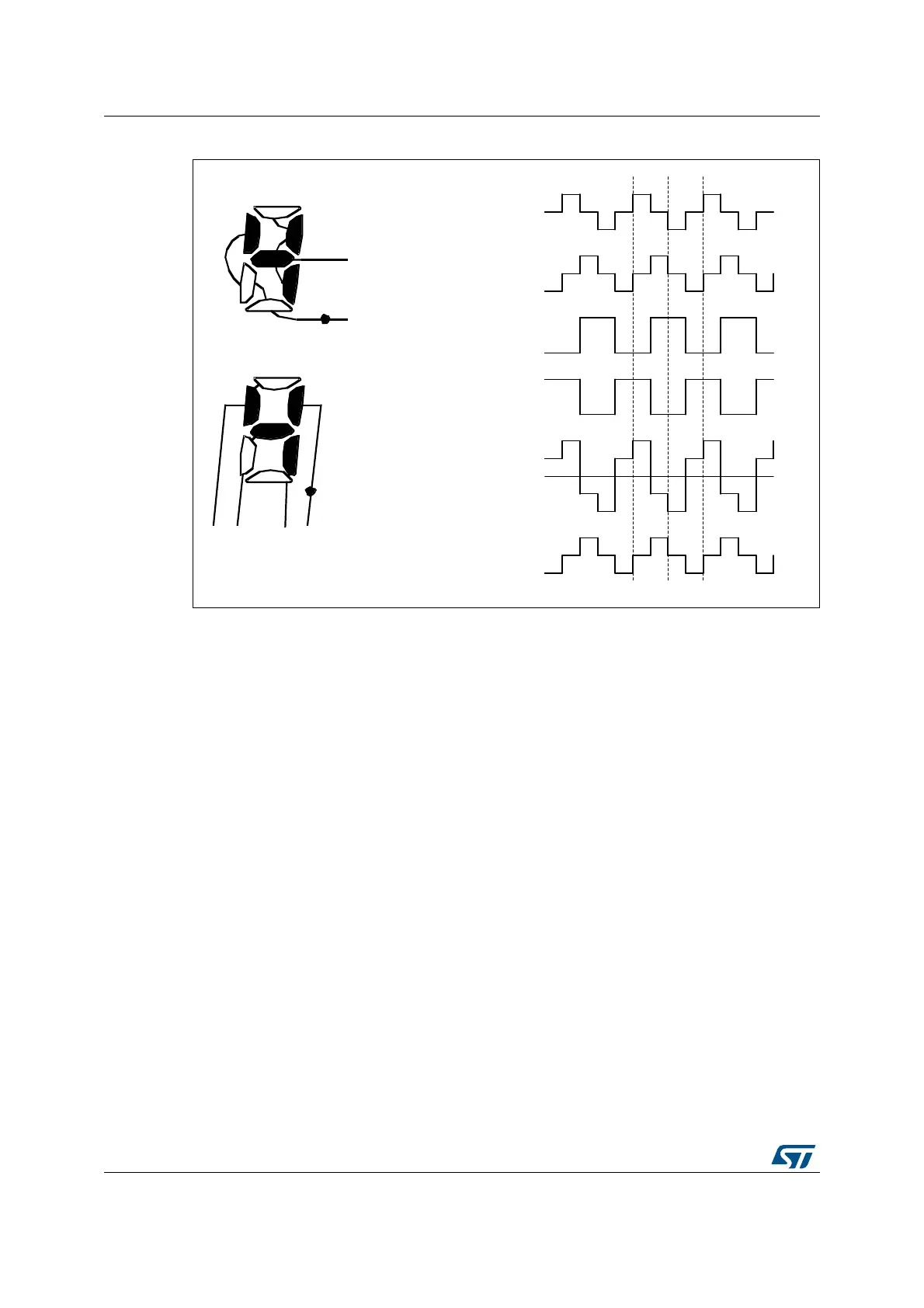

Figure 175. 1/2 duty, 1/2 bias

25.3.4 Segment driver

The segment driver block controls the SEG lines according to the pixel data coming from the

8 to 1 mux driven in each phase by the common driver block.

In the case of 1/4 or 1/8 duty

When COM[0] is active, the pixel information (active/inactive) related to the pixel connected

to COM[0] (content of the first two LCD_RAM locations) goes through the 8 to 1 mux.

The SEG[n] pin n [0 to 43] is driven to V

SS

(indicating pixel n is active when COM[0] is

active) in phase 0 of the odd frame.

The SEG[n] pin is driven to V

LCD

in phase 0 of the even frame. If pixel n is inactive then the

SEG[n] pin is driven to 2/3 (2/4) V

LCD

in the odd frame or 1/3 (2/4) V

LCD

in the even frame

(current inversion in V

LCD

pad) (see Figure 172).

In case of 1/2 bias, if the pixel is inactive the SEG[n] pin is driven to V

LCD

in the odd and to

V

SS

in the even frame.

When the LCD controller is disabled (LCDEN bit cleared in the LCD_CR register) then the

SEG lines are pulled down to V

SS

.

069

9

9

9

3,1

&20

/LTXLGFU\VWDOGLVSOD\

DQGWHUPLQDOFRQQHFWLRQ

&20

6(*

6(*

6(*

6(*

&206(*

QRQVHOHFWHGZDYHIRUP

&20

3,1

&20

9

9

9

3,1

6(*

9

9

3,1

6(*

9

9

&206(*

VHOHFWHGZDYHIRUP

9

9

9

9

9

9

9

9

Loading...

Loading...