Analog-to-digital converters (ADC) RM0351

614/1830 DocID024597 Rev 5

Refer to Section 2.2.2: Memory map and register boundary addresses for the register

boundary addresses.

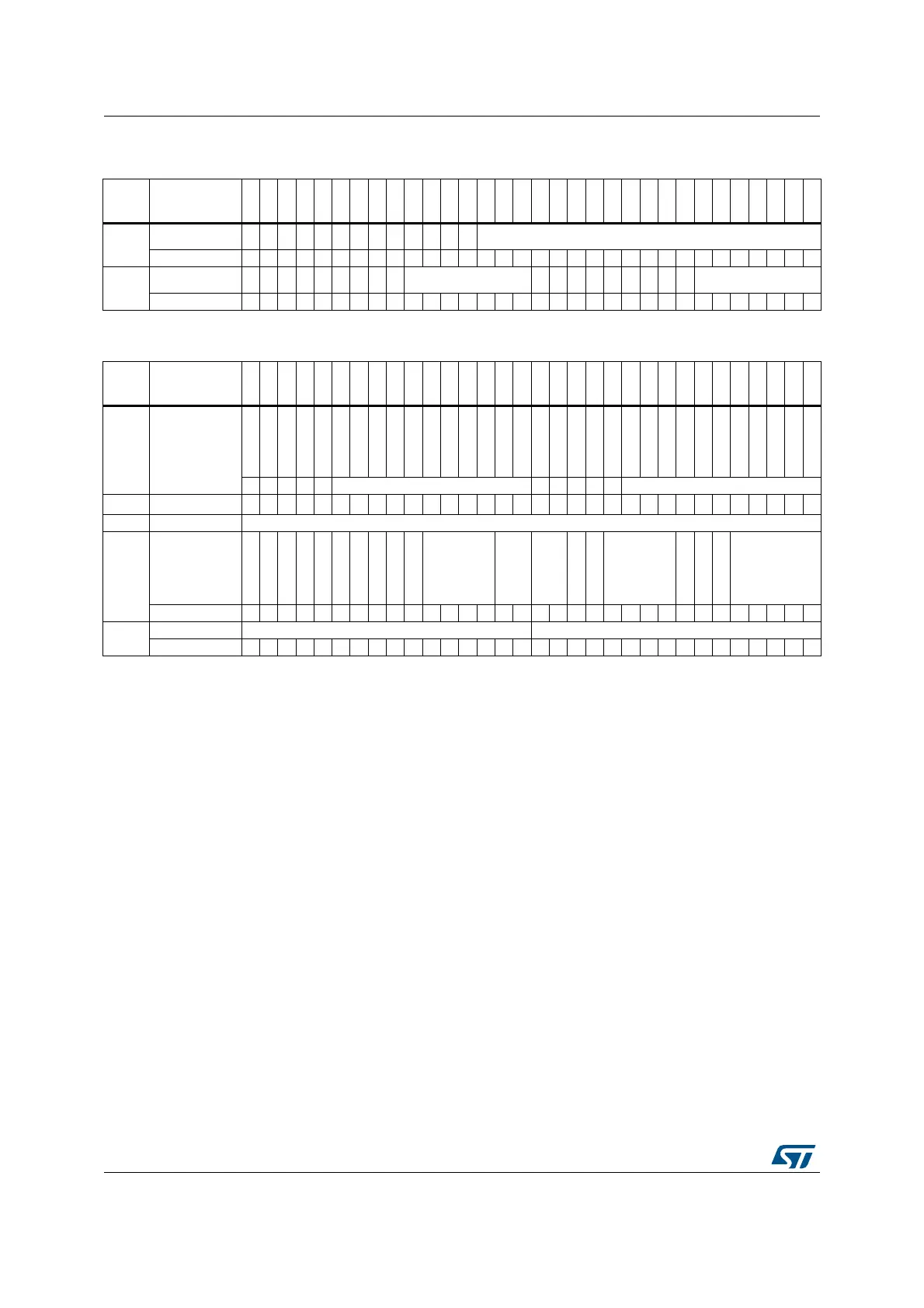

0xB0

ADC_DIFSEL

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

DIFSEL[18:0]

Reset value

0000000000000000000

0xB4

ADC_CALFACT

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CALFACT_D[6:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CALFACT_S[6:0]

Reset value

0000000 0000000

Table 119. ADC register map and reset values for each ADC (offset=0x000

for master ADC, 0x100 for slave ADC) (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

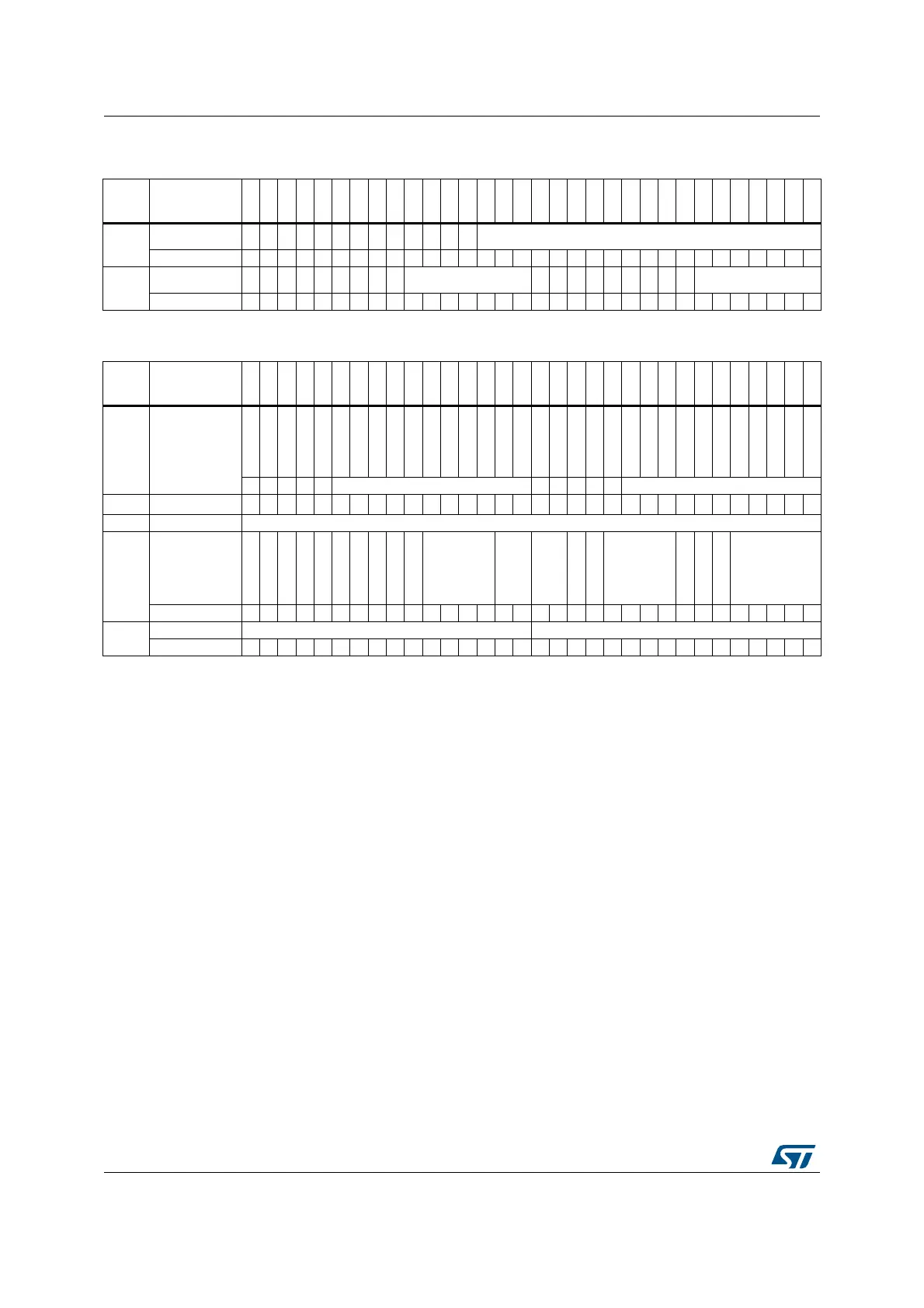

Table 120. ADC register map and reset values (master and slave ADC

common registers) offset =0x300)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00 ADC_CSR

Res.

Res.

Res.

Res.

Res.

JQOVF_SLV

AWD3_SLV

AWD2_SLV

AWD1_SLV

JEOS_SLV

JEOC_SLV

OVR_SLV

EOS_SLV

EOC_SLV

EOSMP_SLV

ADRDY_SLV

Res.

Res.

Res.

Res.

Res.

JQOVF_MST

AWD3_MST

AWD2_MST

AWD1_MST

JEOS_MST

JEOC_MST

OVR_MST

EOS_MST

EOC_MST

EOSMP_MST

ADRDY_MST

slave ADC2 master ADC1

Reset value

0

0000000

0

00

0

0000000

0

00

0x04 Reserved Res.

0x08

ADC_CCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CH18SEL

CH17SEL

VREFEN

PRESC[3:0]

CKMODE[1:0]

MDMA[1:0]

DMACFG

Res.

DELAY[3:0]

Res.

Res.

Res.

DUAL[4:0]

Reset value 000000000000 0000 00000

0x0C

ADC_CDR RDATA_SLV[15:0] RDATA_MST[15:0]

Reset value 00000000000000000000000000000000

Loading...

Loading...