DocID024597 Rev 5 537/1830

RM0351 Analog-to-digital converters (ADC)

614

18.4.23 End of conversion, end of sampling phase (EOC, JEOC, EOSMP)

The ADC notifies the application for each end of regular conversion (EOC) event and each

injected conversion (JEOC) event.

The ADC sets the EOC flag as soon as a new regular conversion data is available in the

ADC_DR register. An interrupt can be generated if bit EOCIE is set. EOC flag is cleared by

the software either by writing 1 to it or by reading ADC_DR.

The ADC sets the JEOC flag as soon as a new injected conversion data is available in one

of the ADC_JDRy register. An interrupt can be generated if bit JEOCIE is set. JEOC flag is

cleared by the software either by writing 1 to it or by reading the corresponding ADC_JDRy

register.

The ADC also notifies the end of Sampling phase by setting the status bit EOSMP (for

regular conversions only). EOSMP flag is cleared by software by writing 1 to it. An interrupt

can be generated if bit EOSMPIE is set.

18.4.24 End of conversion sequence (EOS, JEOS)

The ADC notifies the application for each end of regular sequence (EOS) and for each end

of injected sequence (JEOS) event.

The ADC sets the EOS flag as soon as the last data of the regular conversion sequence is

available in the ADC_DR register. An interrupt can be generated if bit EOSIE is set. EOS

flag is cleared by the software either by writing 1 to it.

The ADC sets the JEOS flag as soon as the last data of the injected conversion sequence is

complete. An interrupt can be generated if bit JEOSIE is set. JEOS flag is cleared by the

software either by writing 1 to it.

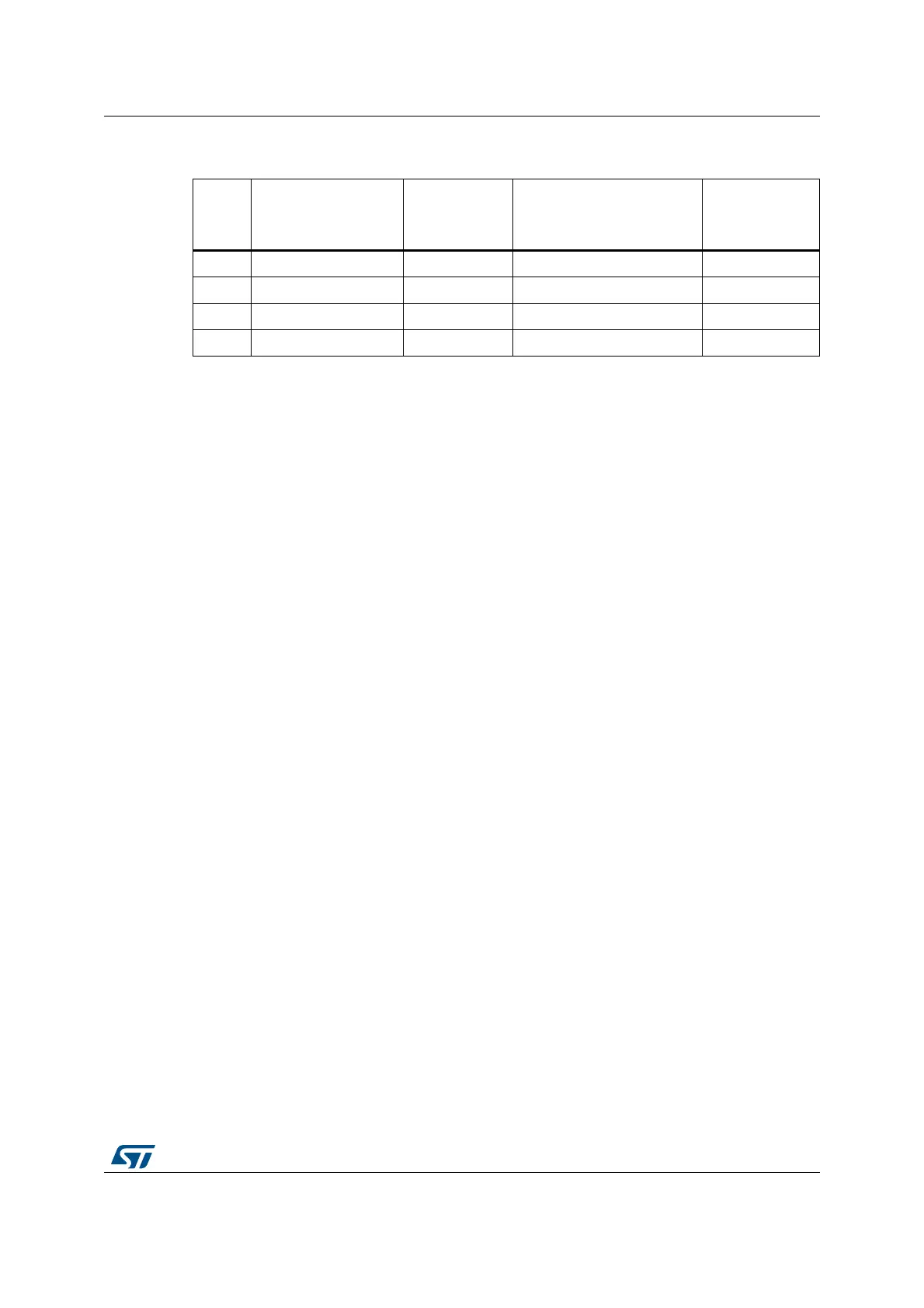

Table 109. T

SAR

timings depending on resolution

RES

(bits)

T

SAR

(ADC clock cycles)

T

SAR

(ns) at

F

ADC

=80 MHz

T

CONV

(ADC clock cycles)

(with Sampling Time=

2.5 ADC clock cycles)

T

CONV

(ns) at

F

ADC

=80 MHz

12 12.5 ADC clock cycles 156.25 ns 15 ADC clock cycles 187.5 ns

10 10.5 ADC clock cycles 131.25 ns 13 ADC clock cycles 162.5 ns

8 8.5 ADC clock cycles 106.25 ns 11 ADC clock cycles 137.5 ns

6 6.5 ADC clock cycles 81.25 ns 9 ADC clock cycles 112.5 ns

Loading...

Loading...