DocID024597 Rev 5 281/1830

RM0351 Clock recovery system (CRS) (only valid for STM32L496xx/4A6xx devices)

289

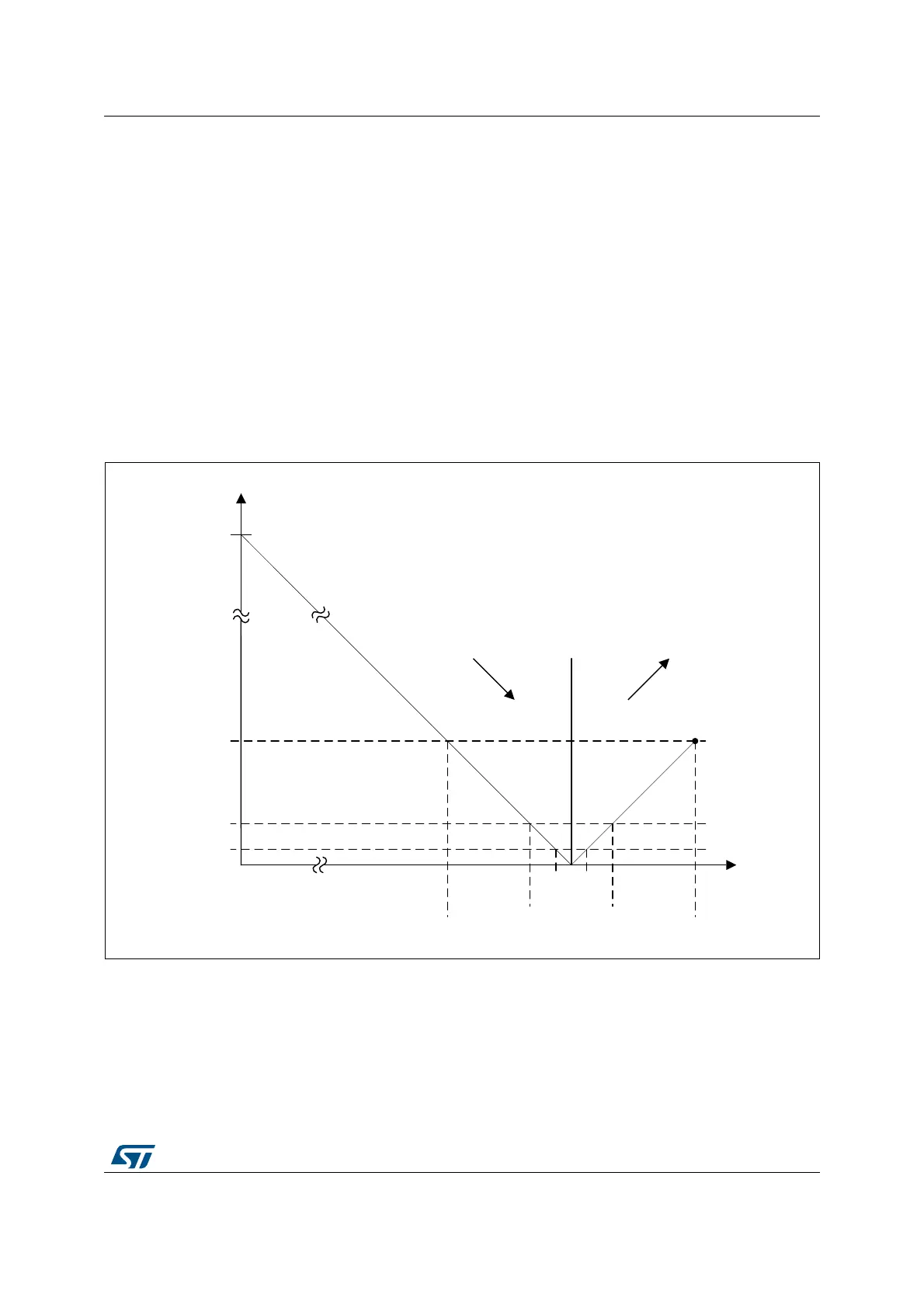

7.3.3 Frequency error measurement

The frequency error counter is a 16-bit down/up counter which is reloaded with the RELOAD

value on each SYNC event. It starts counting down till it reaches the zero value, where the

ESYNC (expected synchronization) event is generated. Then it starts counting up to the

OUTRANGE limit where it eventually stops (if no SYNC event is received) and generates a

SYNCMISS event. The OUTRANGE limit is defined as the frequency error limit (FELIM field

of the CRS_CFGR register) multiplied by 128.

When the SYNC event is detected, the actual value of the frequency error counter and its

counting direction are stored in the FECAP (frequency error capture) field and in the FEDIR

(frequency error direction) bit of the CRS_ISR register. When the SYNC event is detected

during the downcounting phase (before reaching the zero value), it means that the actual

frequency is lower than the target (and so, that the TRIM value should be incremented),

while when it is detected during the upcounting phase it means that the actual frequency is

higher (and that the TRIM value should be decremented).

Figure 22. CRS counter behavior

&56FRXQWHUYDOXH

5(/2$'

2875$1*(

[)(/,0

:$51,1*/,0,7

[)(/,0

72/(5$1&(/,0,7

)(/,0

6<1&(55

6<1&:$51

6<1&2.

6<1&:$51

6<1&0,66

'RZQ

8S

)UHTXHQF\

HUURUFRXQWHU

VWRSSHG

7ULPPLQJDFWLRQ

&56HYHQW

06Y9

(6<1&

Loading...

Loading...