Liquid crystal display controller (LCD) RM0351

760/1830 DocID024597 Rev 5

25.3.2 Frequency generator

This clock source must be stable in order to obtain accurate LCD timing and hence

minimize DC voltage offset across LCD segments. The input clock LCDCLK can be divided

by any value from 1 to 2

15

x 31 (see Section 25.6.2: LCD frame control register (LCD_FCR)

on page 780). The frequency generator consists of a prescaler (16-bit ripple counter) and a

16 to 31 clock divider. The PS[3:0] bits, in the LCD_FCR register, select LCDCLK divided by

2

PS[3:0]

. If a finer resolution rate is required, the DIV[3:0] bits, in the LCD_FCR register, can

be used to divide the clock further by 16 to 31. In this way you can roughly scale the

frequency, and then fine-tune it by linearly scaling the clock with the counter. The output of

the frequency generator block is f

ck_div

which constitutes the time base for the entire LCD

controller. The ck_div frequency is equivalent to the LCD phase frequency, rather than the

frame frequency (they are equal only in case of static duty). The frame frequency (f

frame

) is

obtained from f

ck_div

by dividing it by the number of active common terminals (or by

multiplying it for the duty). Thus the relation between the input clock frequency (f

LCDCLK

) of

the frequency generator and its output clock frequency f

ck_div

is:

This makes the frequency generator very flexible. An example of frame rate calculation is

shown in Table 160.

The frame frequency must be selected to be within a range of around ~30 Hz to ~100 Hz

and is a compromise between power consumption and the acceptable refresh rate. In

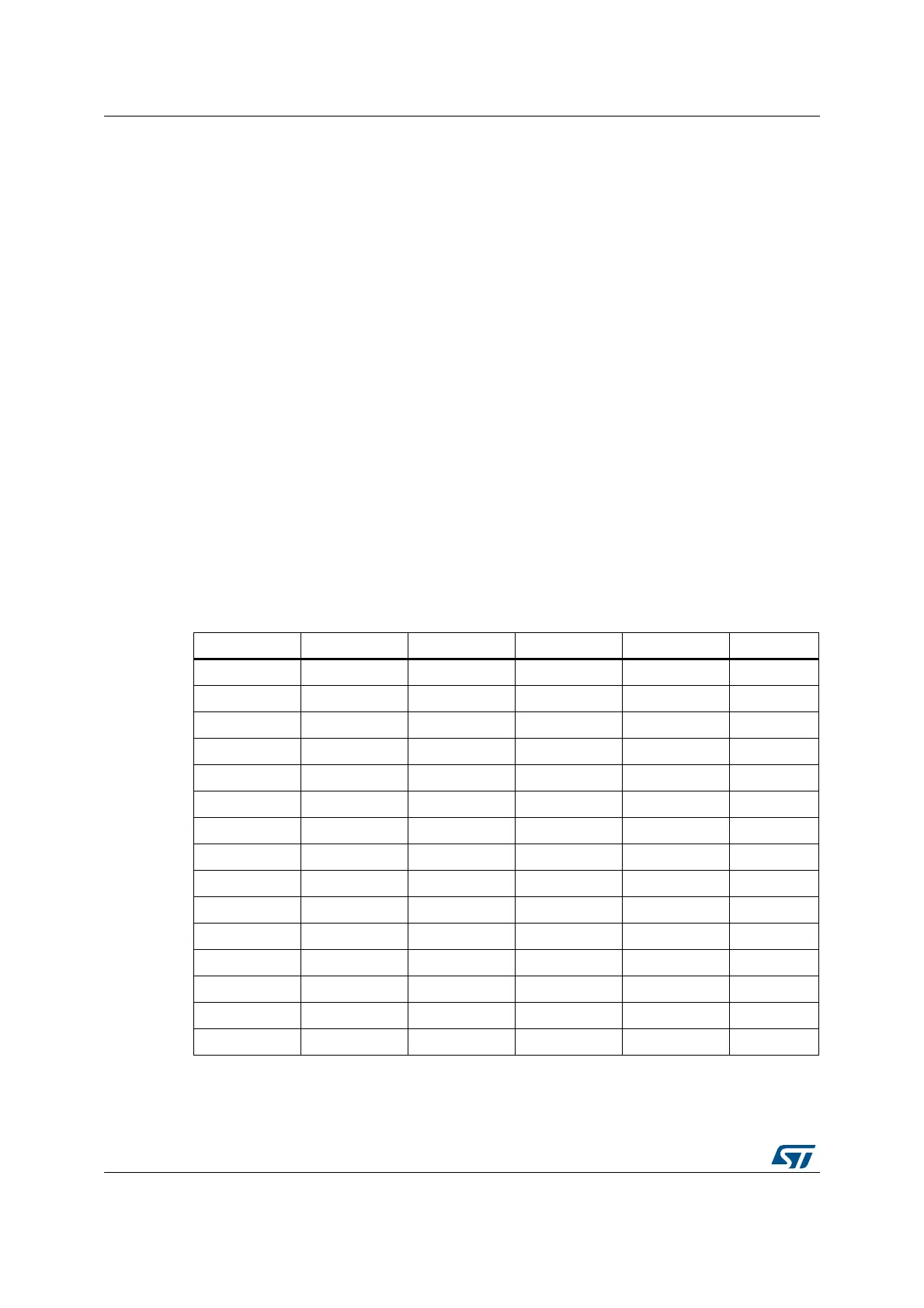

Table 160. Example of frame rate calculation

LCDCLK PS[3:0] DIV[3:0] Ratio Duty f

frame

32.768 kHz 3 1 136 1/8 30.12 Hz

32.768 kHz 4 1 272 1/4 30.12 Hz

32.768 kHz 4 6 352 1/3 31.03 Hz

32.768 kHz 5 1 544 1/2 30.12 Hz

32.768 kHz 6 1 1088 static 30.12 Hz

32.768 kHz 1 4 40 1/8 102.40 Hz

32.768 kHz 2 4 80 1/4 102.40 Hz

32.768 kHz 2 11 108 1/3 101.14 Hz

32.768 kHz 3 4 160 1/2 102.40 Hz

32.768 kHz 4 4 320 static 102.40 Hz

1.00 MHz 6 3 1216 1/8 102.80 Hz

1.00 MHz 7 3 2432 1/4 102.80 Hz

1.00 MHz 7 10 3328 1/3 100.16 Hz

1.00 MHz 8 3 4864 1/2 102.80 Hz

1.00 MHz 9 3 9728 static 102.80 Hz

f

ckdiv

f

LCDCLK

2

PS

16 DIV+()×

--------------------------------------------- -=

Loading...

Loading...