DocID024597 Rev 5 571/1830

RM0351 Analog-to-digital converters (ADC)

614

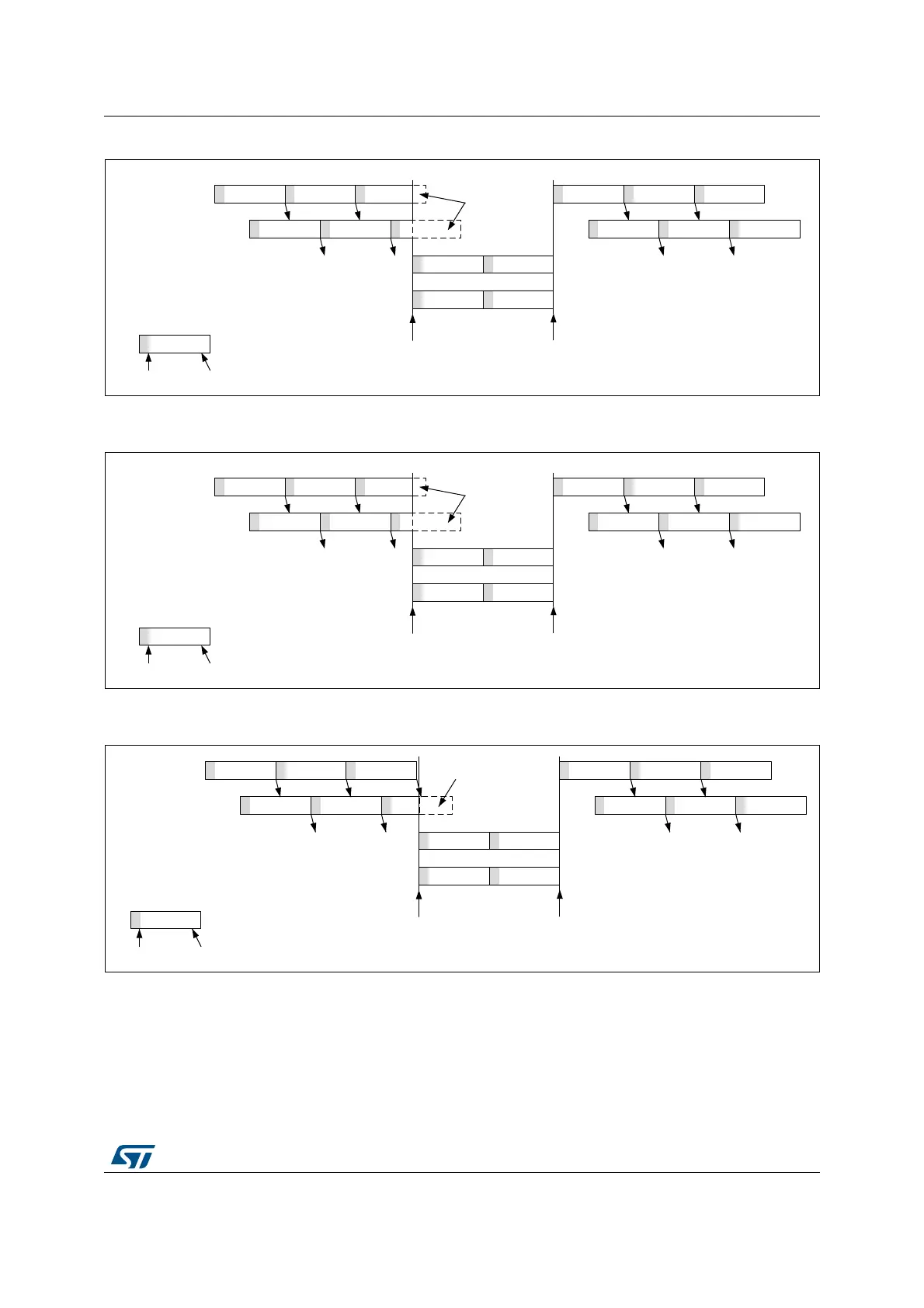

Figure 128. Interleaved single channel CH0 with injected sequence CH11, CH12

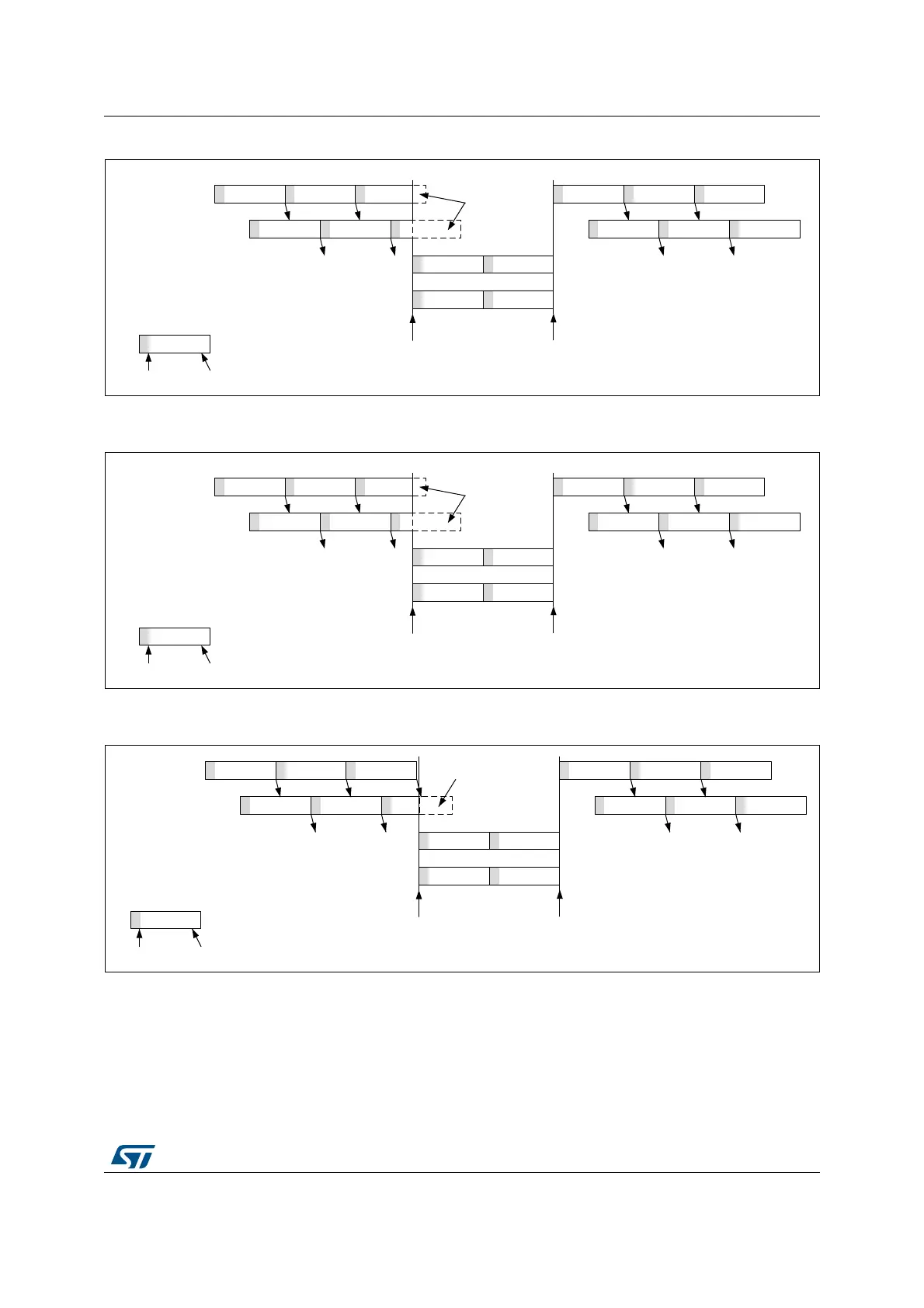

Figure 129. Two Interleaved channels (CH1, CH2) with injected sequence CH11, CH12

- case 1: Master interrupted first

Figure 130. Two Interleaved channels (CH1, CH2) with injected sequence CH11, CH12

- case 2: Slave interrupted first

DMA requests in dual ADC mode

In all dual ADC modes, it is possible to use two DMA channels (one for the master, one for

the slave) to transfer the data, like in single mode (refer to Figure 131: DMA Requests in

069

/HJHQG

6DPSOLQJ &RQYHUVLRQ

$'&PDVWHU

&+ &+ &+

&+

&+ &+ &+

&+ &+ &+&+ &+ &+$'&VODYH

UHDG

&'5

UHDG

&'5

UHDG

&'5

UHDG

&'5

&+

&+ &+

,QMHFWHGWULJJHU

5HVXPH

DOZD\VUHVWDUWZLWKWKHPDVWHU

&RQYHUVLRQV

DERUWHG

069

/HJHQG

6DPSOLQJ &RQYHUVLRQ

$'&PDVWHU

&+ &+ &+

&+

&+ &+ &+

&+ &+ &+&+ &+ &+$'&VODYH

UHDG

&'5

UHDG

&'5

UHDG

&'5

UHDG

&'5

&+

&+ &+

,QMHFWHGWULJJHU

5HVXPH

DOZD\VUHVWDUWZLWKWKHPDVWHU

&RQYHUVLRQV

DERUWHG

069

/HJHQG

6DPSOLQJ &RQYHUVLRQ

$'&PDVWHU

&+ &+ &+

&+

&+ &+ &+

&+ &+ &+&+ &+ &+$'&VODYH

UHDG

&'5

UHDG

&'5

UHDG

&'5

UHDG

&'5

&+

&+ &+

,QMHFWHGWULJJHU

5HVXPH

DOZD\VUHVWDUWZLWKWKHPDVWHU

&RQYHUVLRQV

DERUWHG

Loading...

Loading...