DocID024597 Rev 5 343/1830

RM0351 Direct memory access controller (DMA)

356

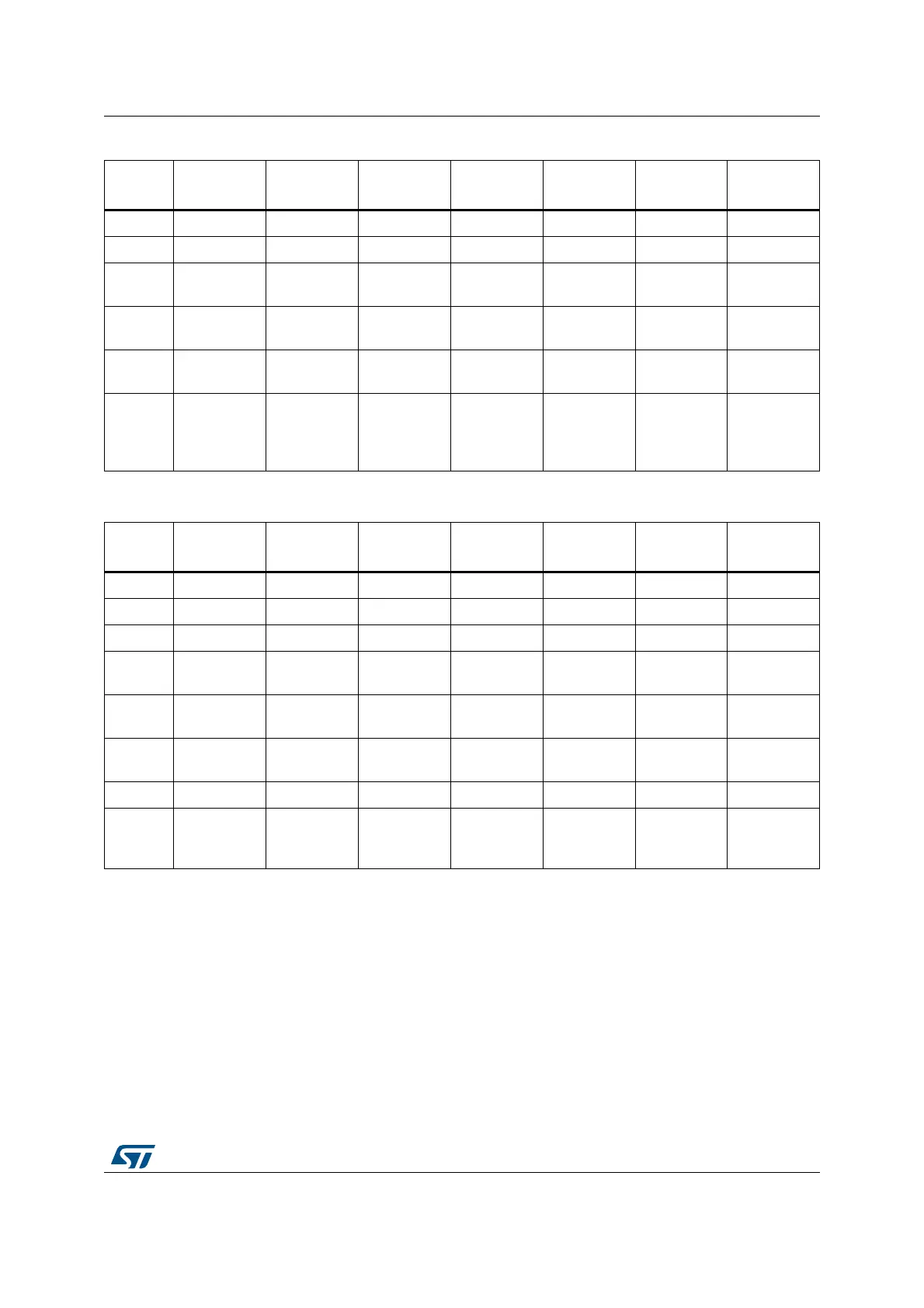

2 - USART3_TX USART3_RX USART1_TX USART1_RX USART2_RX USART2_TX

3 - I2C3_TX I2C3_RX I2C2_TX I2C2_RX I2C1_TX I2C1_RX

4 TIM2_CH3 TIM2_UP

TIM16_CH1

TIM16_UP

- TIM2_CH1

TIM16_CH1

TIM16_UP

TIM2_CH2

TIM2_CH4

5

TIM17_CH1

TIM17_UP

TIM3_CH3

TIM3_CH4

TIM3_UP

TIM7_UP.

DAC2

QUADSPI

TIM3_CH1

TIM3_TRIG

TIM17_CH1

TIM17_UP

6 TIM4_CH1 -

TIM6_UP

DAC1

TIM4_CH2 TIM4_CH3 - TIM4_UP

7 - TIM1_CH1 TIM1_CH2

TIM1_CH4

TIM1_TRIG

TIM1_COM

TIM15_CH1

TIM15_UP

TIM15_TRIG

TIM15_COM

TIM1_UP TIM1_CH3

Table 45. Summary of the DMA1 requests for each channel (continued)

Request.

number

Channel 1 Channel 2 Channel 3 Channel 4 Channel 5 Channel 6 Channel 7

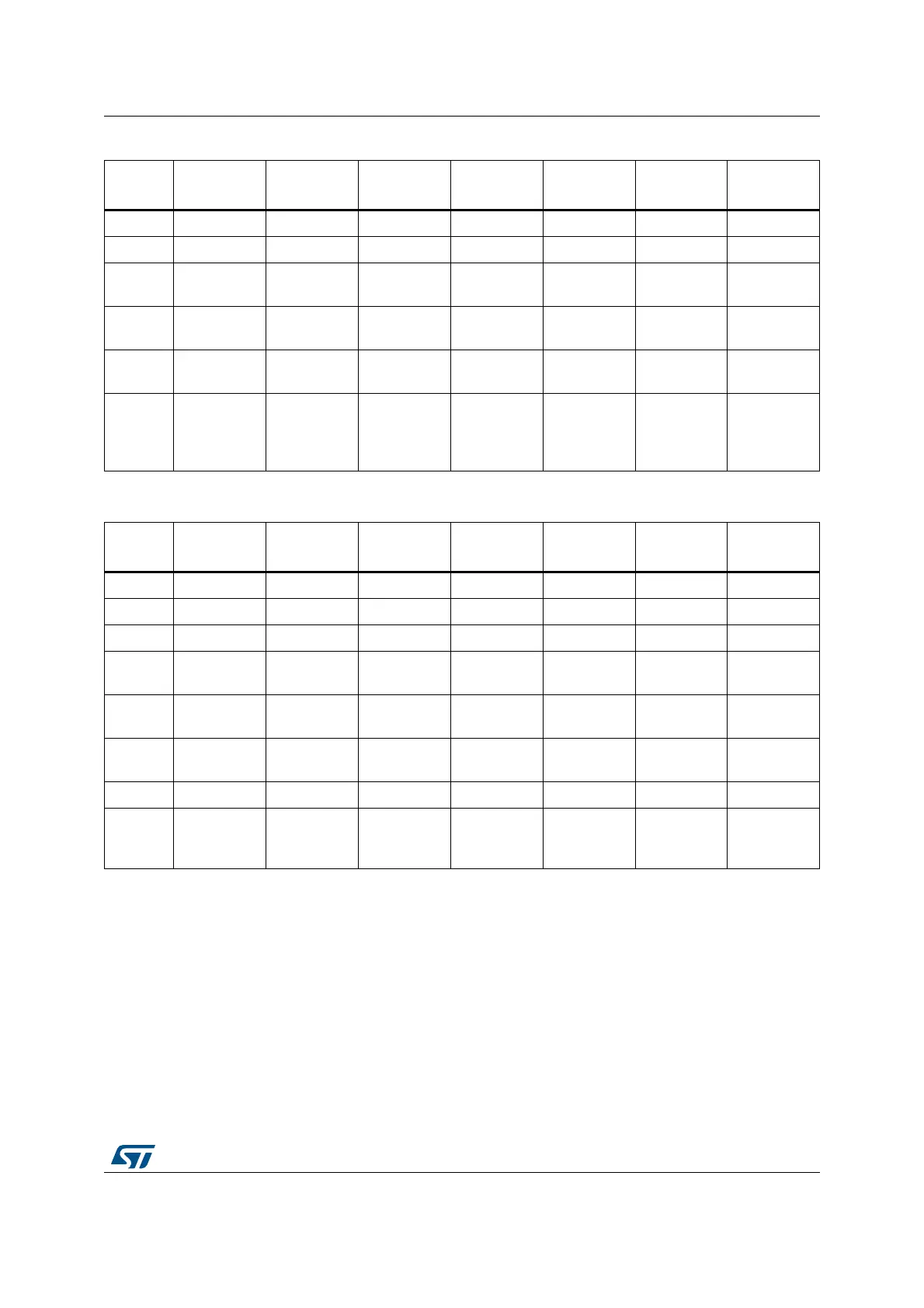

Table 46. Summary of the DMA2 requests for each channel

Request.

number

Channel 1 Channel 2 Channel 3 Channel 4 Channel 5 Channel 6 Channel 7

0 I2C4_RX I2C4_TX ADC1 ADC2 ADC3 DCMI -

1 SAI1_A SAI1_B SAI2_A SAI2_B - SAI1_A SAI1_B

2 UART5_TX UART5_RX UART4_TX - UART4_RX USART1_TX USART1_RX

3 SPI3_RX SPI3_TX -

TIM6_UP

DAC1

TIM7_UP

DAC2

- QUADSPI

4 SWPMI1_RX SWPMI1_TX SPI1_RX SPI1_TX DCMI

LPUART1_

TX

LPUART1_

RX

5

TIM5_CH4

TIM5_TRIG

TIM5_CH3

TIM5_UP

- TIM5_CH2 TIM5_CH1 I2C1_RX I2C1_TX

6 AES_IN AES_OUT AES_OUT - AES_IN - HASH_IN

7

TIM8_CH3

TIM8_UP

TIM8_CH4

TIM8_TRIG

TIM8_COM

- SDMMC1 SDMMC1 TIM8_CH1 TIM8_CH2

Loading...

Loading...