DocID024597 Rev 5 441/1830

RM0351 Flexible static memory controller (FSMC)

471

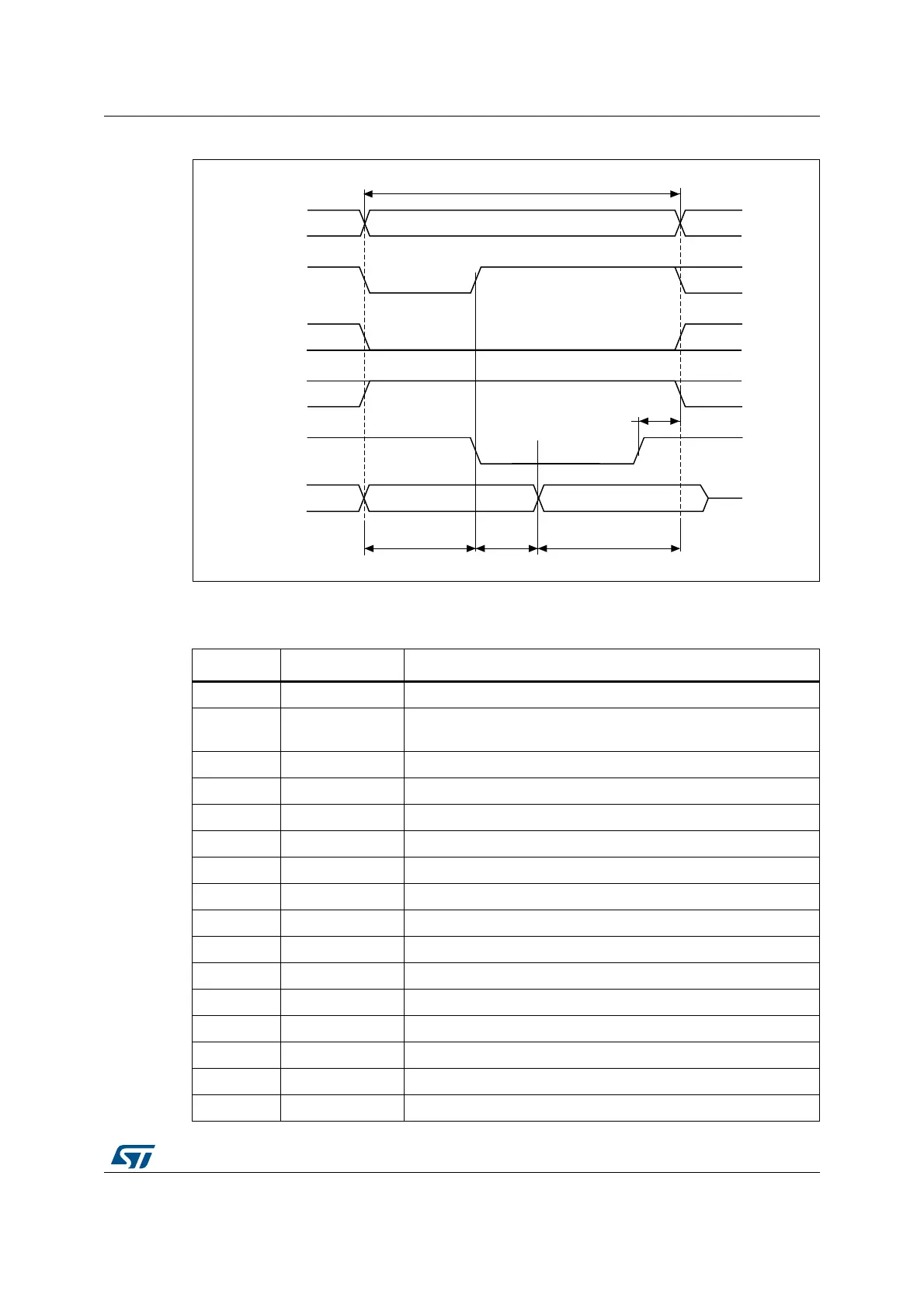

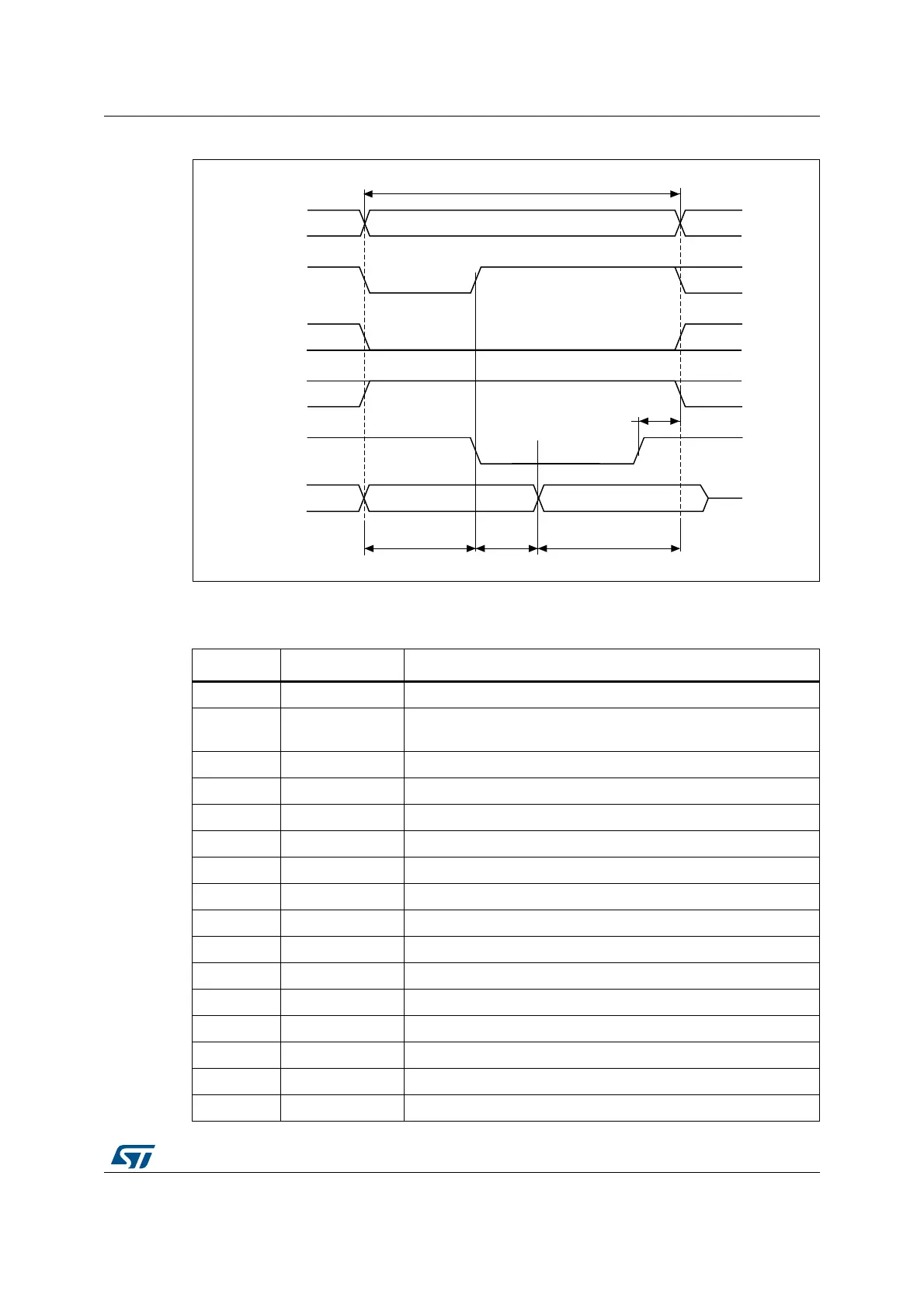

Figure 50. Muxed write access waveforms

The difference with ModeD is the drive of the lower address byte(s) on the data bus.

Table 86. FMC_BCRx bit fields

Bit number Bit name Value to set

31:22 Reserved 0x000

21 WFDIS

As needed (this bit is reserved for STM32L475xx/476xx/486xx

devices)

20 CCLKEN As needed

19 CBURSTRW 0x0 (no effect in asynchronous mode)

18:16 CPSIZE 0x0 (no effect in asynchronous mode)

15 ASYNCWAIT Set to 1 if the memory supports this feature. Otherwise keep at 0.

14 EXTMOD 0x0

13 WAITEN 0x0 (no effect in asynchronous mode)

12 WREN As needed

11 WAITCFG Don’t care

10 Reserved 0x0

9 WAITPOL Meaningful only if bit 15 is 1

8 BURSTEN 0x0

7 Reserved 0x1

6 FACCEN 0x1

5:4 MWID As needed

069

$>@

12(

0HPRU\WUDQVDFWLRQ

1([

1:(

1$'9

+&/.

$''6(7

+&/.F\FOHV

'$7$67

+&/.F\FOHV

$''+/'

+&/.F\FOHV

$'>@ GDWDGULYHQE\)0&

/RZHUDGGUHVV

Loading...

Loading...