DocID024597 Rev 5 705/1830

RM0351 Digital filter for sigma delta modulators (DFSDM)

756

24.4.3 DFSDM reset and clocks

DFSDM on-off control

The DFSDM interface is globally enabled by setting DFSDMEN=1 in the

DFSDM_CH0CFGR1 register. Once DFSDM is globally enabled, all input channels (y=0..7)

and digital filters DFSDM_FLTx (x=0..3) start to work if their enable bits are set (channel

enable bit CHEN in DFSDM_CHyCFGR1 and DFSDM_FLTx enable bit DFEN in

DFSDM_FLTxCR1).

Digital filter x DFSDM_FLTx (x=0..3) is enabled by setting DFEN=1 in the

DFSDM_FLTxCR1 register. Once DFSDM_FLTx is enabled (DFEN=1), both Sinc

x

digital

filter unit and integrator unit are reinitialized.

By clearing DFEN, any conversion which may be in progress is immediately stopped and

DFSDM_FLTx is put into stop mode. All register settings remain unchanged except

DFSDM_FLTxAWSR and DFSDM_FLTxISR (which are reset).

Channel y (y=0..7) is enabled by setting CHEN=1 in the DFSDM_CHyCFGR1 register.

Once the channel is enabled, it receives serial data from the external modulator or

parallel internal data sources (ADCs

(a)

or CPU/DMA wire from memory).

DFSDM must be globally disabled (by DFSDMEN=0 in DFSDM_CH0CFGR1) before

stopping the system clock to enter in the STOP mode of the device.

DFSDM clocks

The internal DFSDM clock f

DFSDMCLK

, which is used to drive the channel transceivers,

digital processing blocks (digital filter, integrator) and next additional blocks (analog

watchdog, short-circuit detector, extremes detector, control block) is generated by the RCC

block and is derived from the system clock SYSCLK (max. up to f

SYSCLK

= 80 MHz) or

peripheral clock PCLK2 (see DFSDMSEL bit description in Section 6.4.28: Peripherals

independent clock configuration register (RCC_CCIPR)). The DFSDM clock is automatically

stopped in stop mode (if DFEN = 0 for all DFSDM_FLTx, x=0..3).

dfsdm_jtrg9 EXTI11

dfsdm_jtrg10 EXTI15

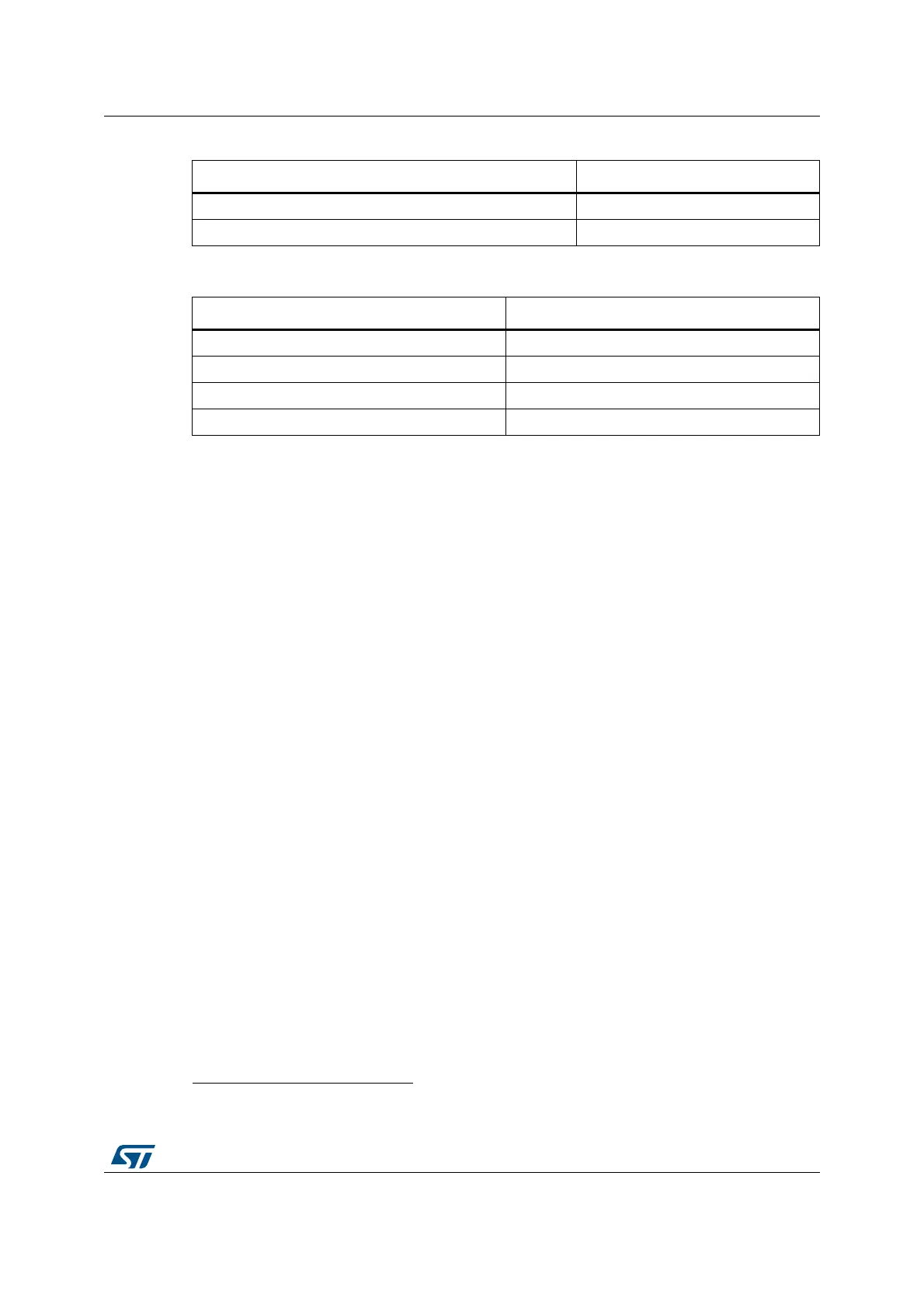

Table 155. DFSDM break connection

Break name Break destination

dfsdm_break[0] TIM1 break

dfsdm_break[1] TIM1 break2

dfsdm_break[2] TIM8 break

dfsdm_break[3] TIM8 break2

Table 154. DFSDM triggers connection (continued)

Trigger name Trigger source

a. STM32L496xx/4A6xx devices only.

Loading...

Loading...