DocID024597 Rev 5 1283/1830

RM0351 Inter-integrated circuit (I2C) interface

1301

DMA must be initialized before setting the START bit. The end of transfer is managed

with the NBYTES counter.

• In slave mode with NOSTRETCH=0, when all data are transferred using DMA, the

DMA must be initialized before the address match event, or in the ADDR interrupt

subroutine, before clearing the ADDR flag.

• If SMBus is supported (see Section 39.3: I2C implementation): the PEC transfer is

managed with the NBYTES counter. Refer to SMBus Slave receiver on page 1274 and

SMBus Master receiver on page 1278.

Note: If DMA is used for reception, the RXIE bit does not need to be enabled.

39.4.17 Debug mode

When the microcontroller enters debug mode (core halted), the SMBus timeout either

continues to work normally or stops, depending on the DBG_I2Cx_SMBUS_TIMEOUT

configuration bits in the DBG module.

39.5 I2C low-power modes

39.6 I2C interrupts

The table below gives the list of I2C interrupt requests.

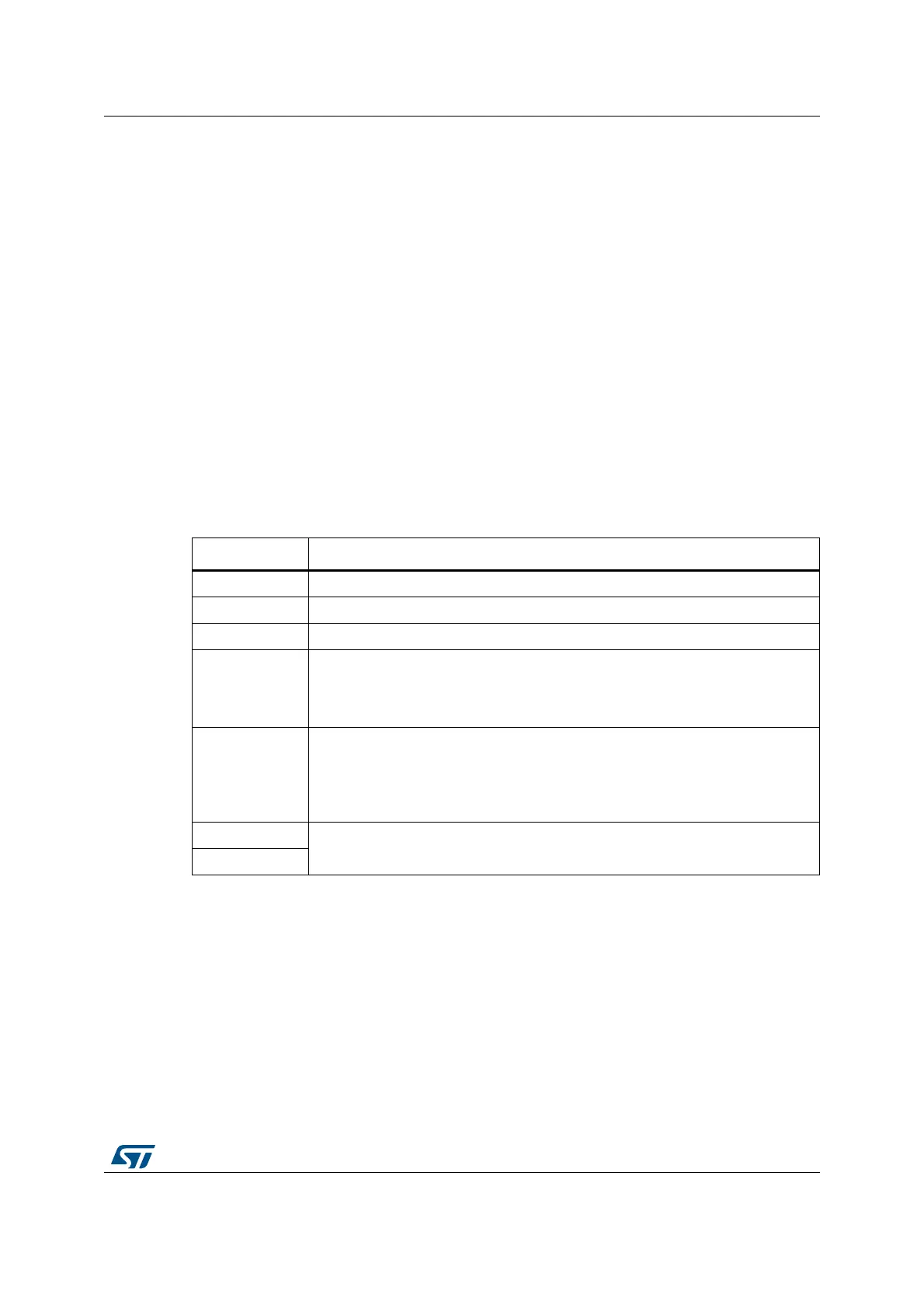

Table 229. Effect of low-power modes on the I2C

Mode Description

Sleep No effect. I2C interrupts cause the device to exit the Sleep mode.

Low-power run No effect.

Low-power sleep No effect. I2C interrupts cause the device to exit the Low-power sleep mode.

Stop 0 / Stop 1

The I2C registers content is kept. If WUPEN = 1 and I2C is clocked by HSI16: the

address recognition is functional. The I2C address match condition causes the

device to exit the Stop 0 and Stop 1 modes. If WUPEN=0: the I2C must be

disabled before entering Stop mode.

Stop 2

The I2C registers content is kept. The I2C1, I2C2 and I2C4

(1)

must be disabled

before entering Stop 2. If WUPEN=1 and I2C3 is clocked by HSI16: the I2C3

address recognition is functional. The I2C3 address match condition causes the

device to exit the Stop mode 2. If WUPEN=0: the I2C3 must be disabled before

entering Stop 2 mode.

1. I2C4 not available on STM32L475xx/476xx/486xxdevices.

Standby

The I2C peripheral is powered down and must be reinitialized after exiting

Standby or Shutdown mode.

Shutdown

Loading...

Loading...