DocID024597 Rev 5 1055/1830

RM0351 General-purpose timers (TIM15/TIM16/TIM17)

1133

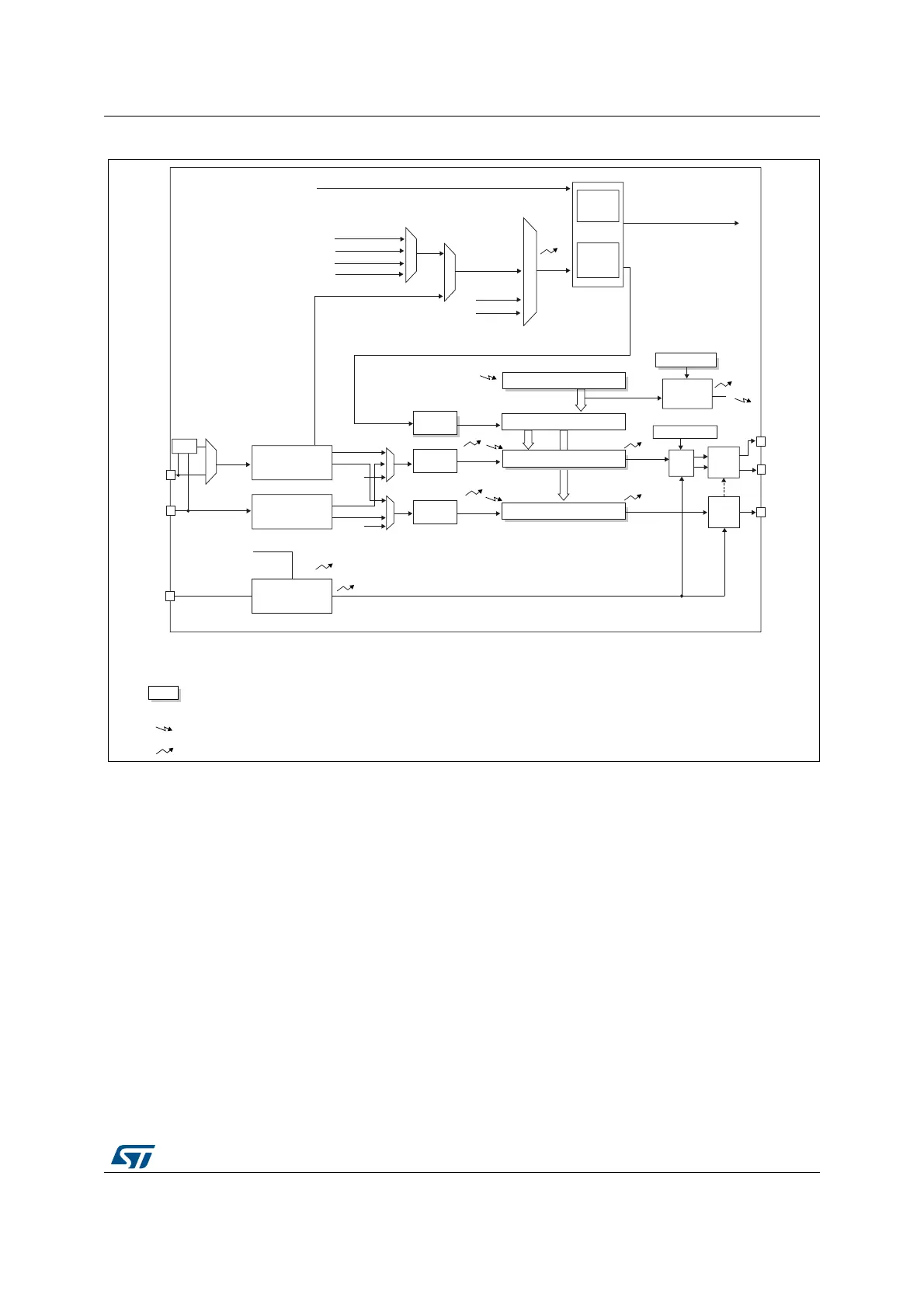

Figure 321. TIM15 block diagram

1. The internal break event source can be:

- A clock failure event generated by CSS. For further information on the CSS, refer to Section 6.2.10: Clock security

system (CSS)

- A PVD output

- SRAM parity error signal

- Cortex

®

-M4 LOCKUP (Hardfault) output

- COMP output

06Y9

8

8

8

&&,

&&,

7ULJJHU

FRQWUROOHU

6WRSFOHDURUXSGRZQ

7,)3

7,)3

,75

,75

,75

75*,

2XWSXW

FRQWURO

'7*

75*2

2&5()

2&5()

5(3UHJLVWHU

8

5HSHWLWLRQ

FRXQWHU

8,

5HVHWHQDEOHXSFRXQW

&.B36&

,&

,&

,&36

,&36

7,)3

7*,

75&

75&

,75

75&

7,)B('

&&,

&&,

7,)3

7,)3

7,)3

7,

7,

7,0[B&+

7,0[B&+

2&

2&

7,0[B&+

7,0[B&+

7,0[B&+1

2&1

WRRWKHUWLPHUV

6ODYH

FRQWUROOHU

PRGH

36&

SUHVFDOHU

&17FRXQWHU

,QWHUQDOFORFN&.B,17

&.B&17

&.B7,0IURP5&&

,75

;25

'7*UHJLVWHUV

,QSXWILOWHU

HGJHGHWHFWRU

&DSWXUH&RPSDUHUHJLVWHU

1RWHV

5HJ

3UHORDGUHJLVWHUVWUDQVIHUUHG

WRDFWLYHUHJLVWHUVRQ8HYHQW

DFFRUGLQJWRFRQWUROELW

(YHQW

,QWHUUXSW'0$RXWSXW

7,0[B%.,1

,QWHUQDOVRXUFHV

6%,)

$XWRUHORDGUHJLVWHU

&DSWXUH&RPSDUHUHJLVWHU

3UHVFDOHU

3UHVFDOHU

,QSXWILOWHU

HGJHGHWHFWRU

2XWSXW

FRQWURO

%UHDNFLUFXLWU\

%,)

%5.UHTXHVW

Loading...

Loading...