General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0351

1024/1830 DocID024597 Rev 5

1. Configure TIM3 master mode to send its Update Event (UEV) as trigger output

(MMS=010 in the TIM3_CR2 register).

2. Configure the TIM3 period (TIM3_ARR registers).

3. Configure TIM2 to get the input trigger from TIM3 (TS=010 in the TIM2_SMCR

register).

4. Configure TIM2 in trigger mode (SMS=110 in TIM2_SMCR register).

5. Start TIM3 by writing ‘1 in the CEN bit (TIM3_CR1 register).

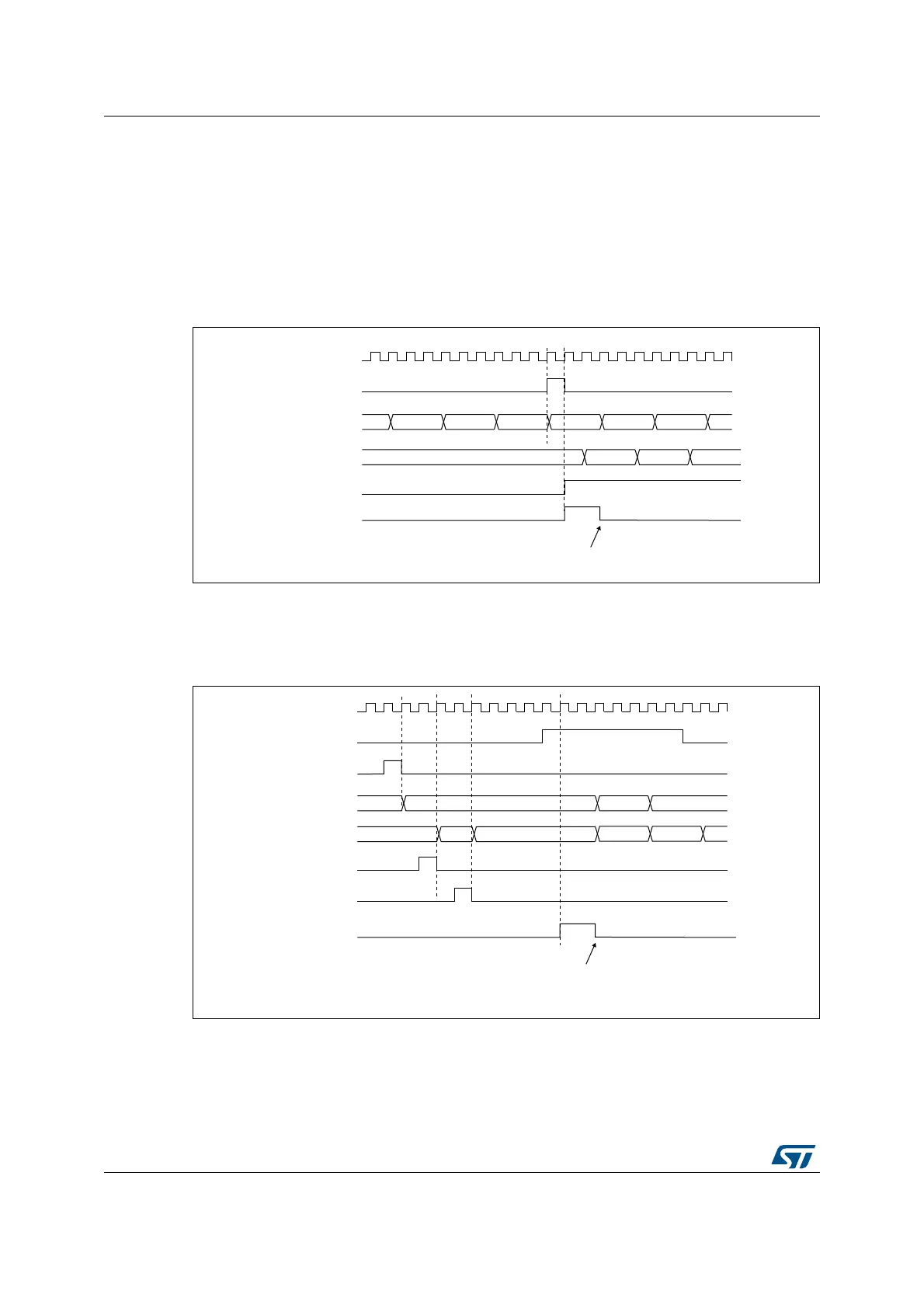

Figure 318. Triggering TIM2 with update of TIM3

As in the previous example, you can initialize both counters before starting counting.

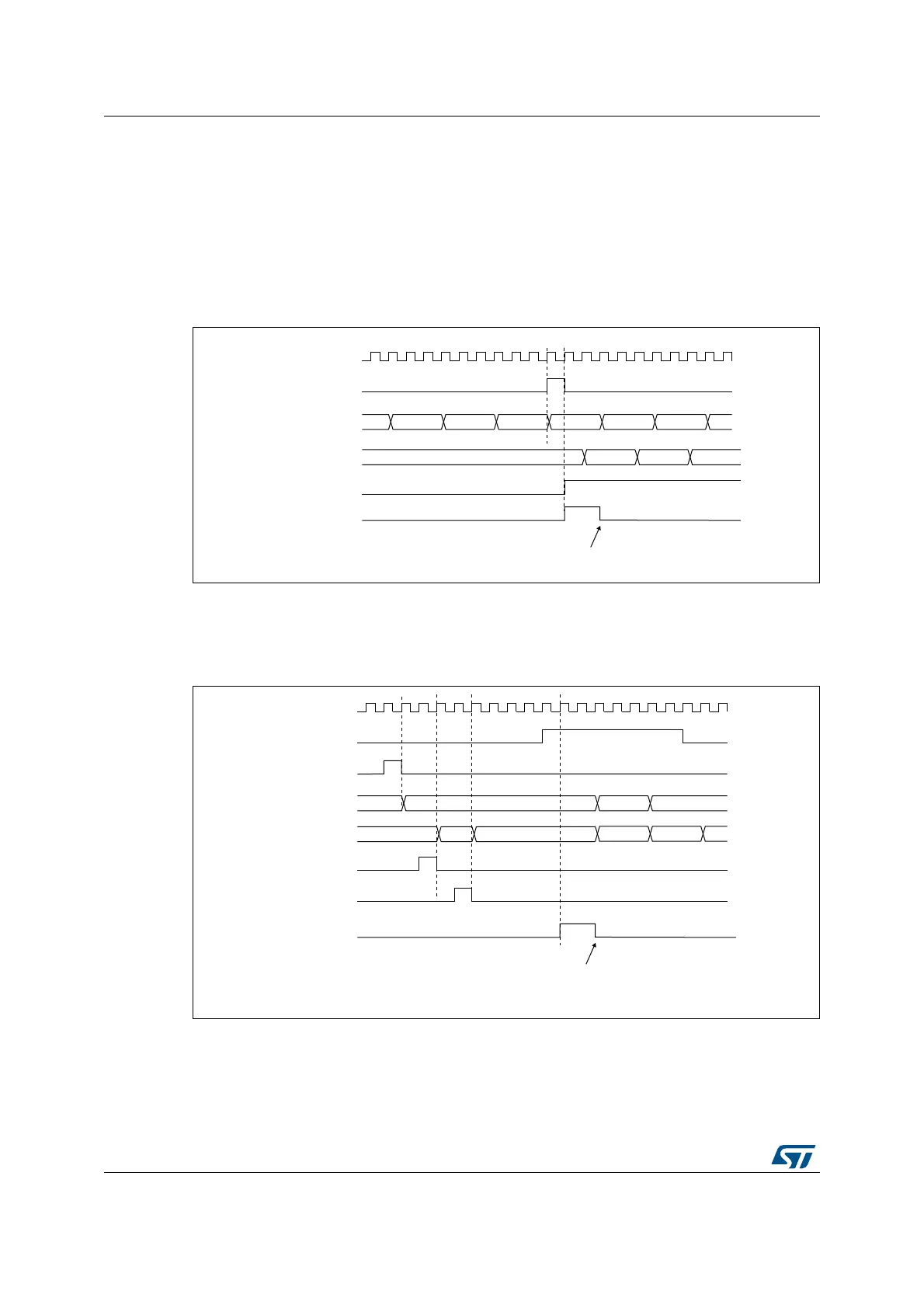

Figure 319 shows the behavior with the same configuration as in Figure 318 but in trigger

mode instead of gated mode (SMS=110 in the TIM2_SMCR register).

Figure 319. Triggering TIM2 with Enable of TIM3

Starting 2 timers synchronously in response to an external trigger

In this example, we set the enable of TIM3 when its TI1 input rises, and the enable of TIM2

with the enable of TIM3. Refer to Figure 315 for connections. To ensure the counters are

069

&.B,17

7,0&17

)'7,0&17

:ULWH7,)

7,0&(1 &17B(1

7,07,)

)( ))

7,08(9

069

&.B,17

7,0&17

7,0&17B,1,7

:ULWH7,)

7,0&(1 &17B(1

7,07,)

(

(

&' ( ($

7,0&17

7,0&17B,1,7

7,0

ZULWH&17

Loading...

Loading...