Inter-integrated circuit (I2C) interface RM0351

1232/1830 DocID024597 Rev 5

The following additional features are also available depending on the product

implementation (see Section 39.3: I2C implementation):

• SMBus specification rev 2.0 compatibility:

– Hardware PEC (Packet Error Checking) generation and verification with ACK

control

– Command and data acknowledge control

– Address resolution protocol (ARP) support

– Host and Device support

– SMBus alert

– Timeouts and idle condition detection

• PMBus rev 1.1 standard compatibility

• Independent clock: a choice of independent clock sources allowing the I2C

communication speed to be independent from the PCLK reprogramming

• Wakeup from Stop mode on address match.

39.3 I2C implementation

This manual describes the full set of features implemented in I2C peripheral. In the

STM32L4x5/STM32L4x6 devices I2C1, I2C2, I2C3 and I2C4 implement the full set of

features as shown in the following table, with the restriction than only I2C3 can wake up

from Stop 2 mode.

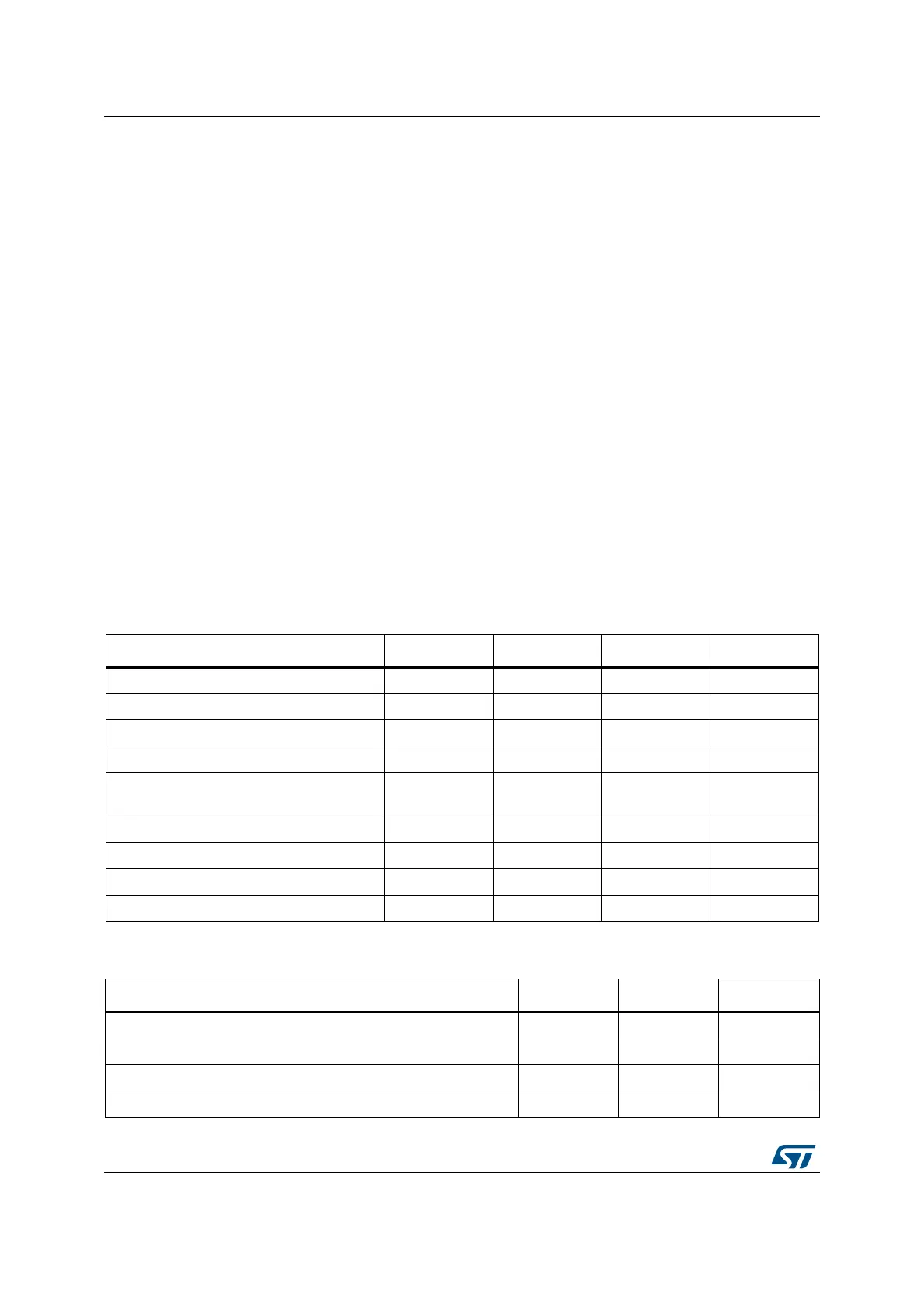

Table 215. STM32L496xx/4A6xx devices I2C implementation

I2C features

(1)

I2C1 I2C2 I2C3 I2C4

7-bit addressing mode XXXX

10-bit addressing mode XXXX

Standard-mode (up to 100 kbit/s) XXXX

Fast-mode (up to 400 kbit/s) XXXX

Fast-mode Plus with 20mA output drive

I/Os (up to 1 Mbit/s)

XXXX

Independent clock XXXX

SMBus XXXX

Wakeup from Stop 1 mode XXXX

Wakeup from Stop 2 mode - - X -

1. X = supported.

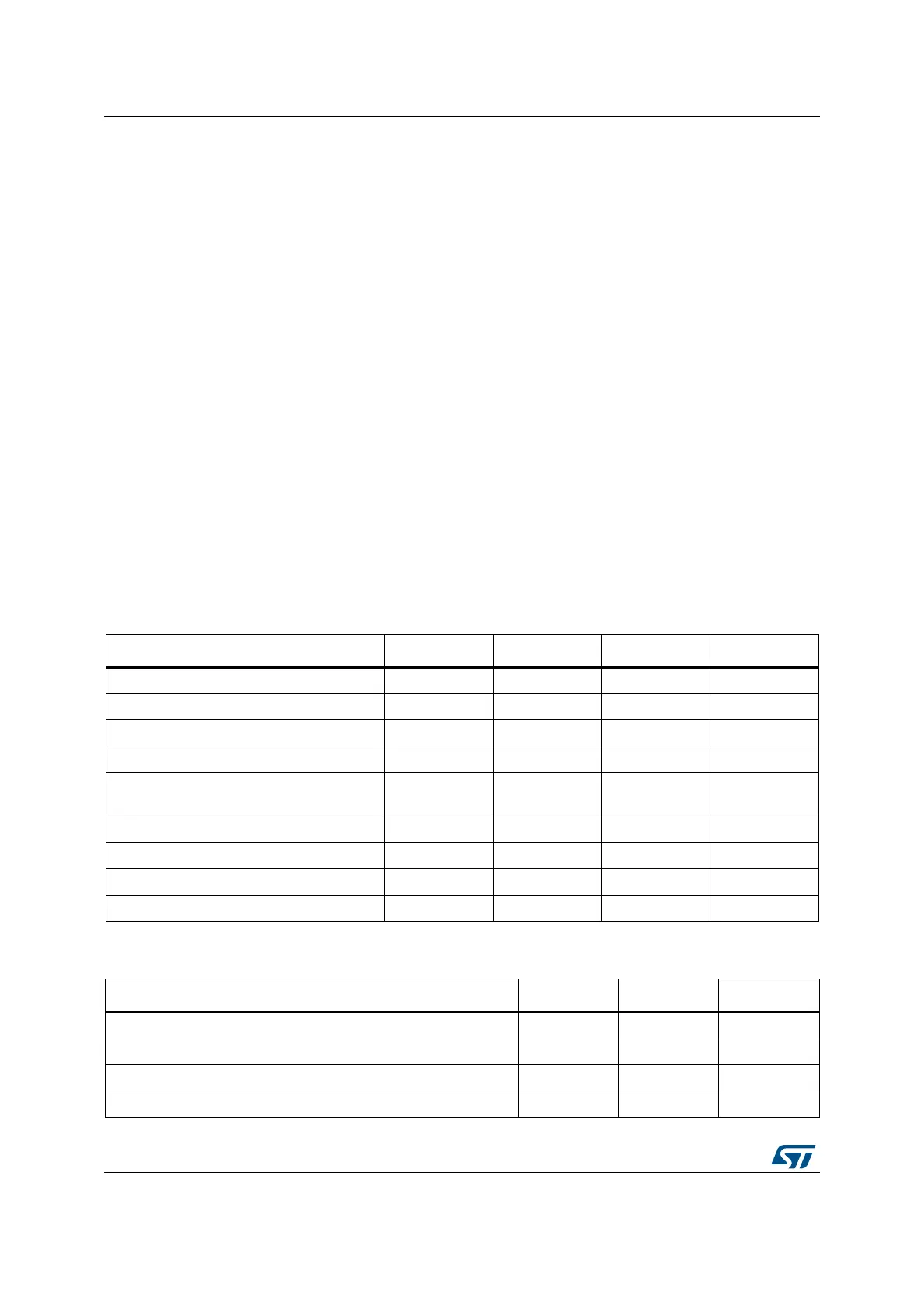

Table 216. STM32L475xx/476xx/486xx devices I2C implementation

I2C features

(1)

I2C1 I2C2 I2C3

7-bit addressing mode X X X

10-bit addressing mode X X X

Standard-mode (up to 100 kbit/s) X X X

Fast-mode (up to 400 kbit/s) X X X

Loading...

Loading...