DocID024597 Rev 5 1241/1830

RM0351 Inter-integrated circuit (I2C) interface

1301

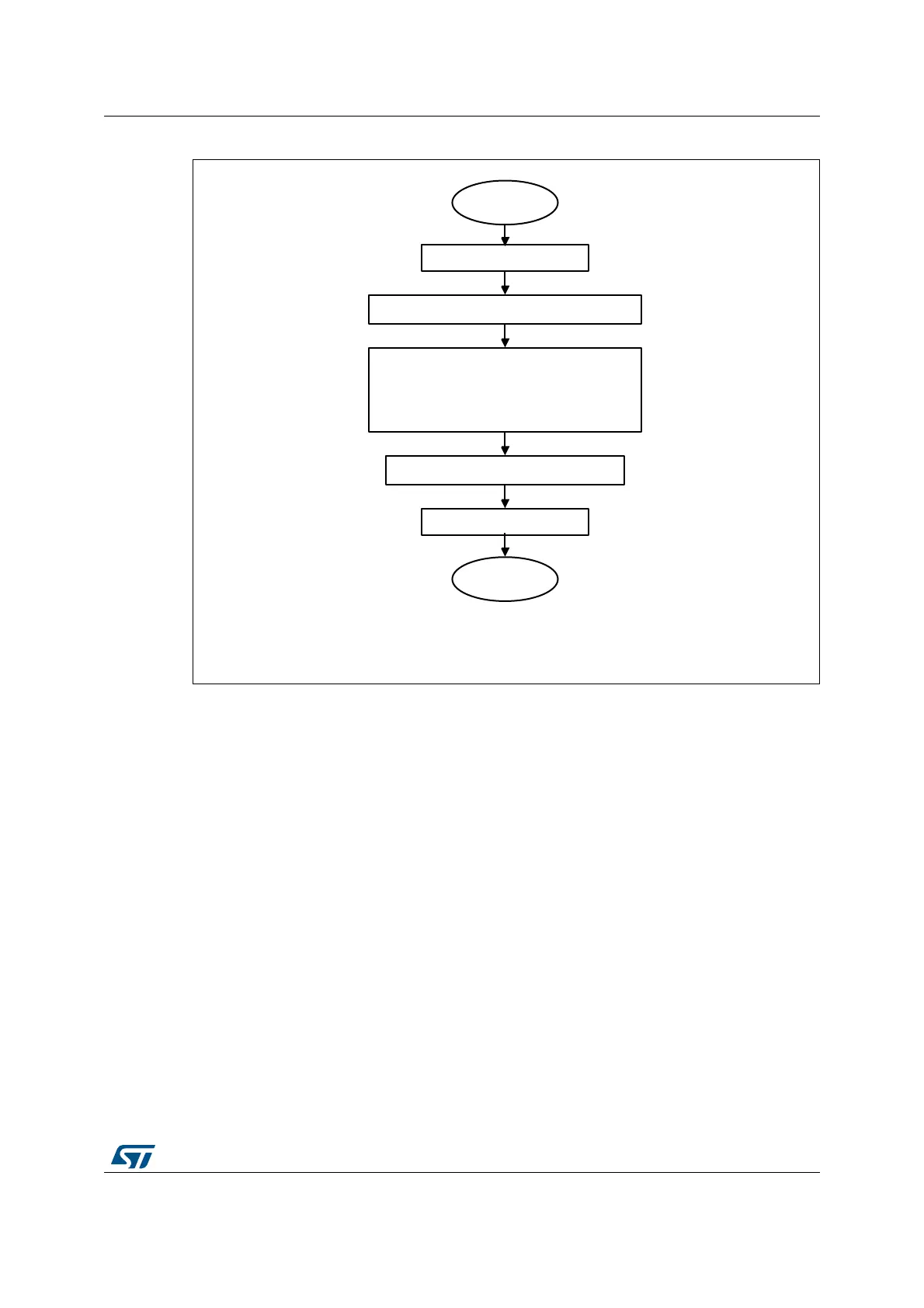

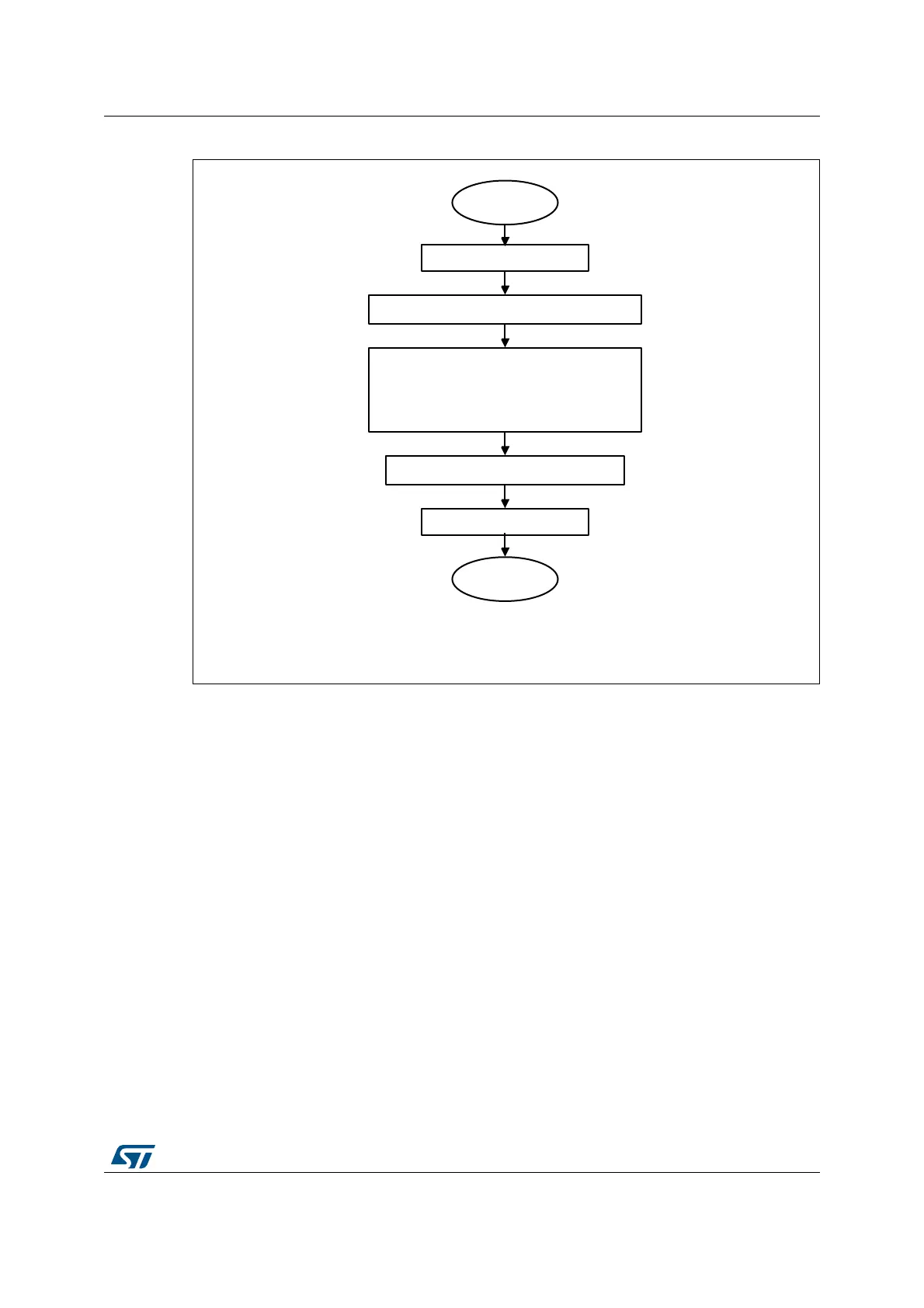

Figure 378. I2C initialization flowchart

39.4.5 Software reset

A software reset can be performed by clearing the PE bit in the I2C_CR1 register. In that

case I2C lines SCL and SDA are released. Internal states machines are reset and

communication control bits, as well as status bits come back to their reset value. The

configuration registers are not impacted.

Here is the list of impacted register bits:

1. I2C_CR2 register: START, STOP, NACK

2. I2C_ISR register: BUSY, TXE, TXIS, RXNE, ADDR, NACKF, TCR, TC, STOPF, BERR,

ARLO, OVR

and in addition when the SMBus feature is supported:

1. I2C_CR2 register: PECBYTE

2. I2C_ISR register: PECERR, TIMEOUT, ALERT

PE must be kept low during at least 3 APB clock cycles in order to perform the software

reset. This is ensured by writing the following software sequence: - Write PE=0 - Check

PE=0 - Write PE=1.

D^ϭϵϴϰϳsϮ

&OHDU3(ELWLQ,&B&5

,QLWLDOVHWWLQJV

&RQILJXUH$1)2))DQG'1)>@LQ,&B&5

&RQILJXUH35(6&>@

6'$'(/>@6&/'(/>@6&/+>@

6&//>@LQ,&B7,0,1*5

&RQILJXUH12675(7&+LQ,&B&5

6HW3(ELWLQ,&B&5

(QG

Loading...

Loading...