DocID024597 Rev 5 579/1830

RM0351 Analog-to-digital converters (ADC)

614

18.5 ADC interrupts

For each ADC, an interrupt can be generated:

• after ADC power-up, when the ADC is ready (flag ADRDY)

• on the end of any conversion for regular groups (flag EOC)

• on the end of a sequence of conversion for regular groups (flag EOS)

• on the end of any conversion for injected groups (flag JEOC)

• on the end of a sequence of conversion for injected groups (flag JEOS)

• when an analog watchdog detection occurs (flag AWD1, AWD2 and AWD3)

• when the end of sampling phase occurs (flag EOSMP)

• when the data overrun occurs (flag OVR)

• when the injected sequence context queue overflows (flag JQOVF)

Separate interrupt enable bits are available for flexibility.

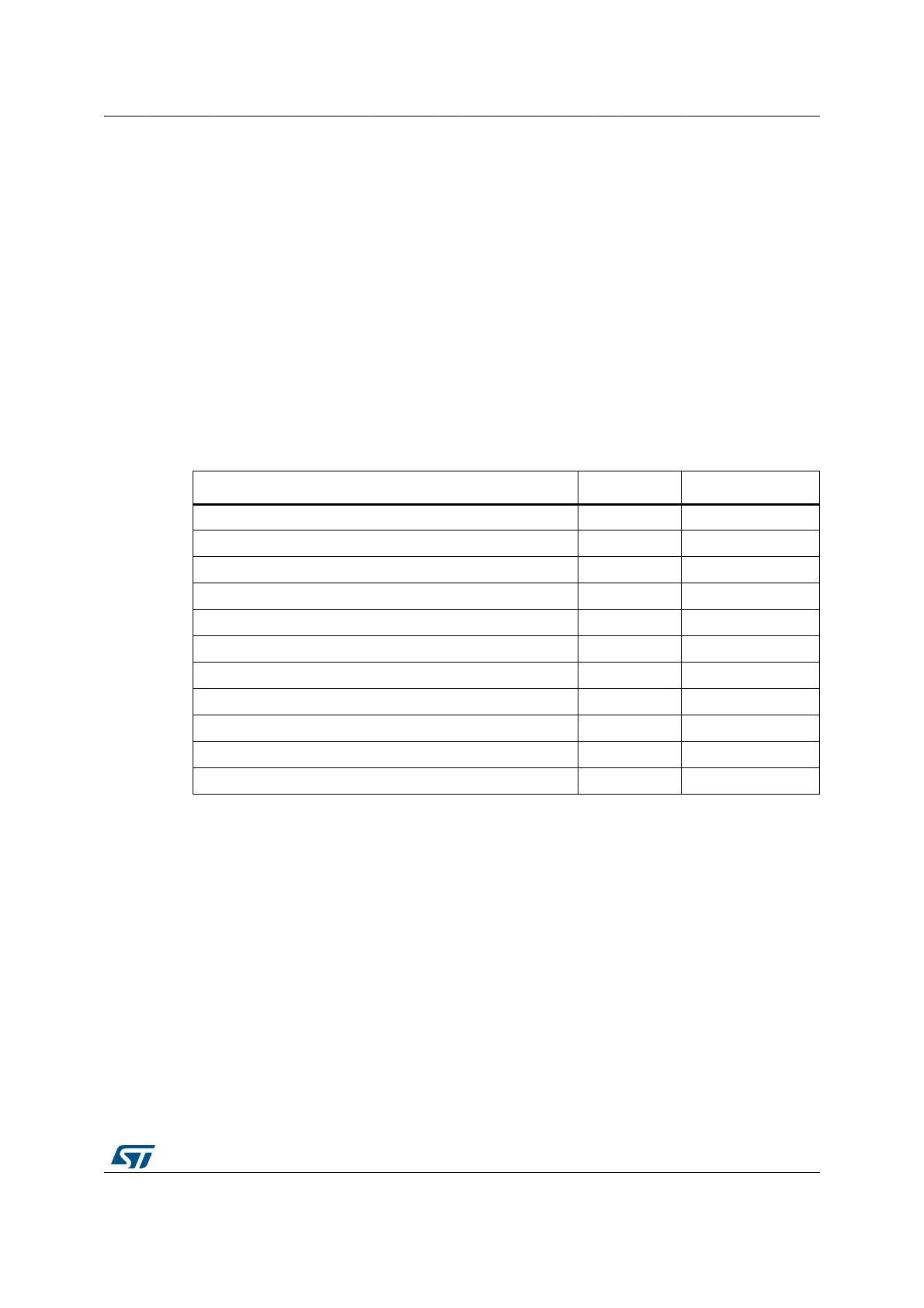

Table 116. ADC interrupts per each ADC

Interrupt event Event flag Enable control bit

ADC ready ADRDY ADRDYIE

End of conversion of a regular group EOC EOCIE

End of sequence of conversions of a regular group EOS EOSIE

End of conversion of a injected group JEOC JEOCIE

End of sequence of conversions of an injected group JEOS JEOSIE

Analog watchdog 1 status bit is set AWD1 AWD1IE

Analog watchdog 2 status bit is set AWD2 AWD2IE

Analog watchdog 3 status bit is set AWD3 AWD3IE

End of sampling phase EOSMP EOSMPIE

Overrun OVR OVRIE

Injected context queue overflows JQOVF JQOVFIE

Loading...

Loading...