DocID024597 Rev 5 825/1830

RM0351 Advanced encryption standard hardware accelerator (AES)

852

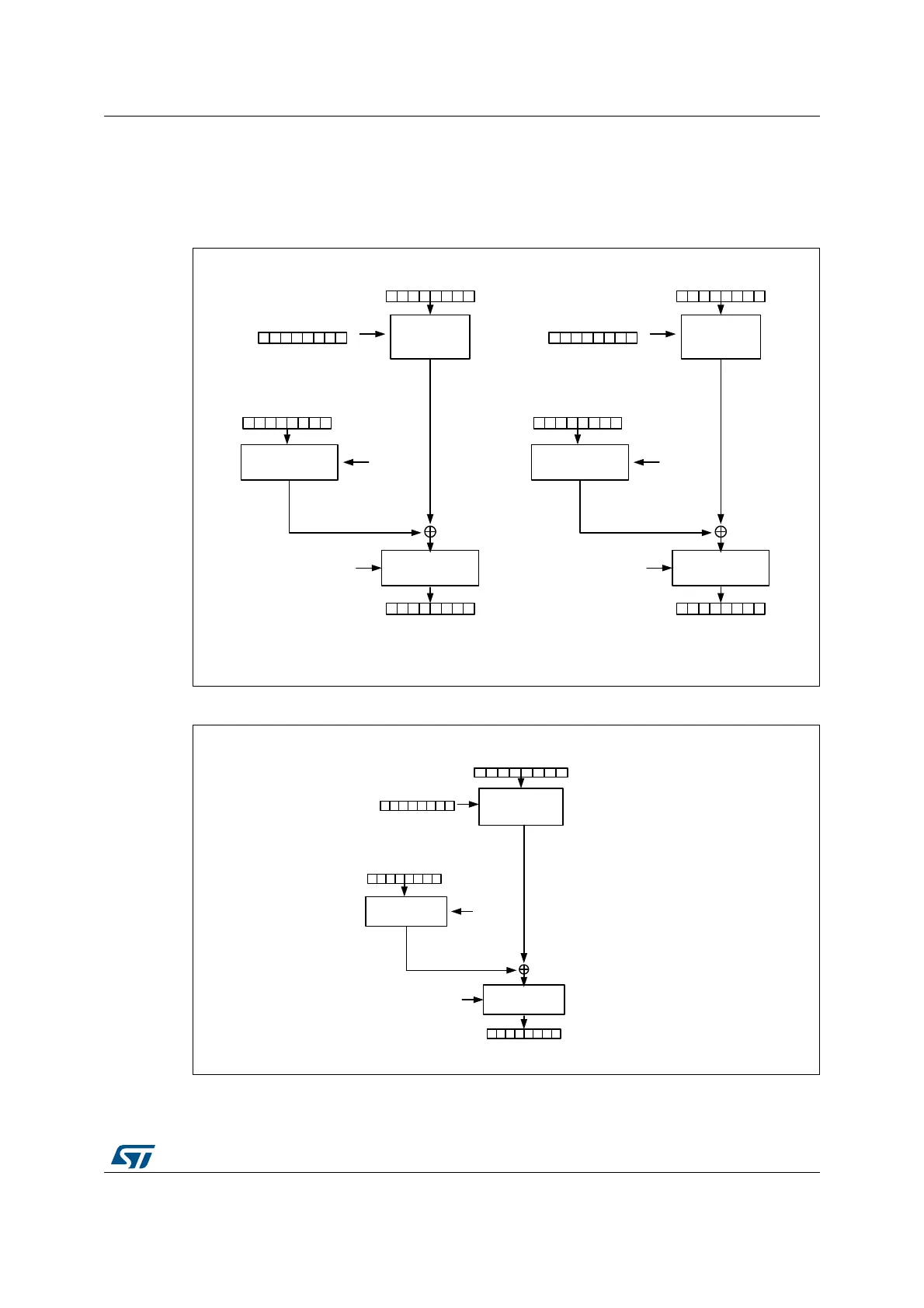

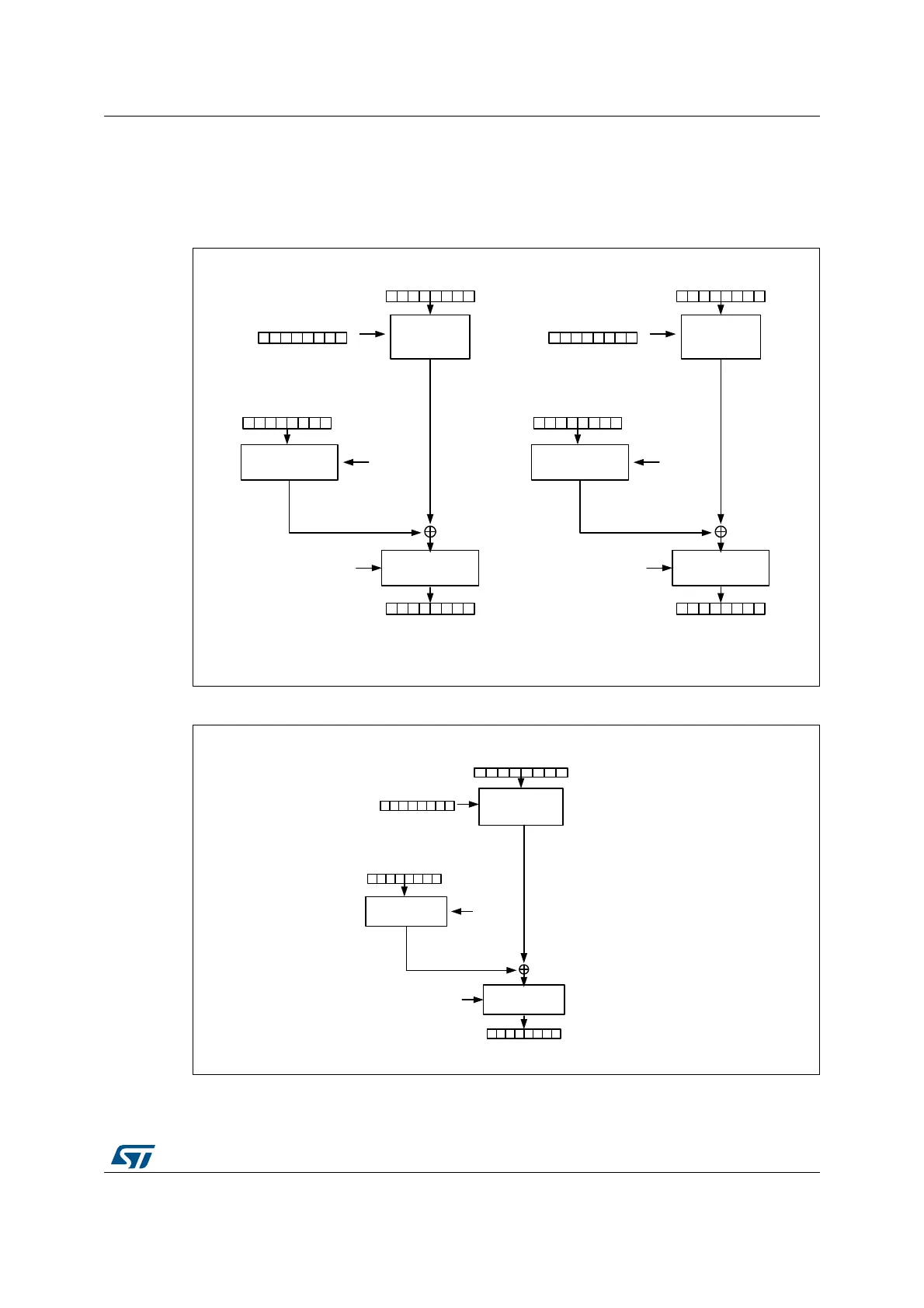

28.5.3 Counter Mode (CTR)

In counter mode, a 32-bit counter is used in addition to a nonce value for the XOR operation

with the cipher text or plain text (refer to Figure 196 and Figure 197).

Figure 196. CTR mode encryption

Figure 197. CTR mode decryption

06

$(6B',153ODLQWH[W

$(6B.(<5[.H\

%ORFNFLSKHU

HQFU\SWLRQ

$(6B,95[

1RQFH FRXQWHU

6ZDS

PDQDJHPHQW

'DWDW\SH>@

$(6B'2875&LSKHUWH[W

6ZDS

PDQDJHPHQW

'DWDW\SH>@

$(6B.(<5[.H\

%ORFNFLSKHU

HQFU\SWLRQ

$(6B,95[

1RQFH

6ZDS

PDQDJHPHQW

'DWDW\SH>@

$(6B'2875&LSKHUWH[W

6ZDS

PDQDJHPHQW

'DWDW\SH>@

$(6B',153ODLQWH[W

FRXQWHU

D^ϭϴϵϰϮsϭ

$(6B',15&LSKHUWH[W

$(6B.(<5[.H\

%ORFNFLSKHU

HQFU\SWLRQ

$(6B,95[

1RQFH FRXQWHU

6ZDS

PDQDJHPHQW

'DWDW\SH

>@

$(6B'28753ODLQWH[W

6ZDS

PDQDJHPHQW

'DWDW\SH>@

Loading...

Loading...