Flexible static memory controller (FSMC) RM0351

444/1830 DocID024597 Rev 5

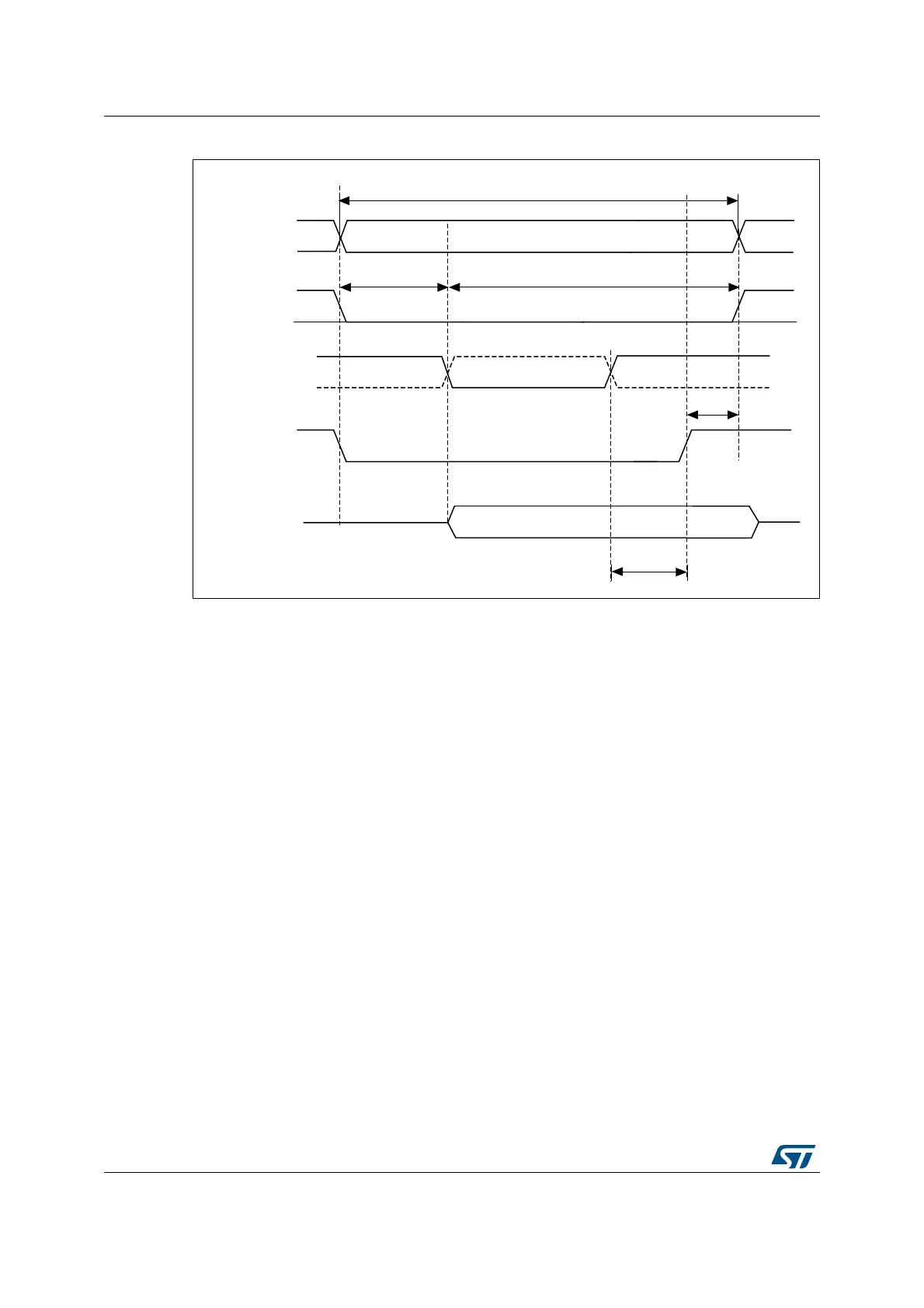

Figure 52. Asynchronous wait during a write access waveforms

1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

16.5.5 Synchronous transactions

The memory clock, FMC_CLK, is a submultiple of HCLK. It depends on the value of

CLKDIV and the MWID/ AHB data size, following the formula given below:

Whatever MWID size: 16 or 8-bit, the FMC_CLK divider ratio is always defined by the

programmed CLKDIV value.

Example:

• If CLKDIV=1, MWID = 16 bits, AHB data size=8 bits, FMC_CLK=HCLK/2.

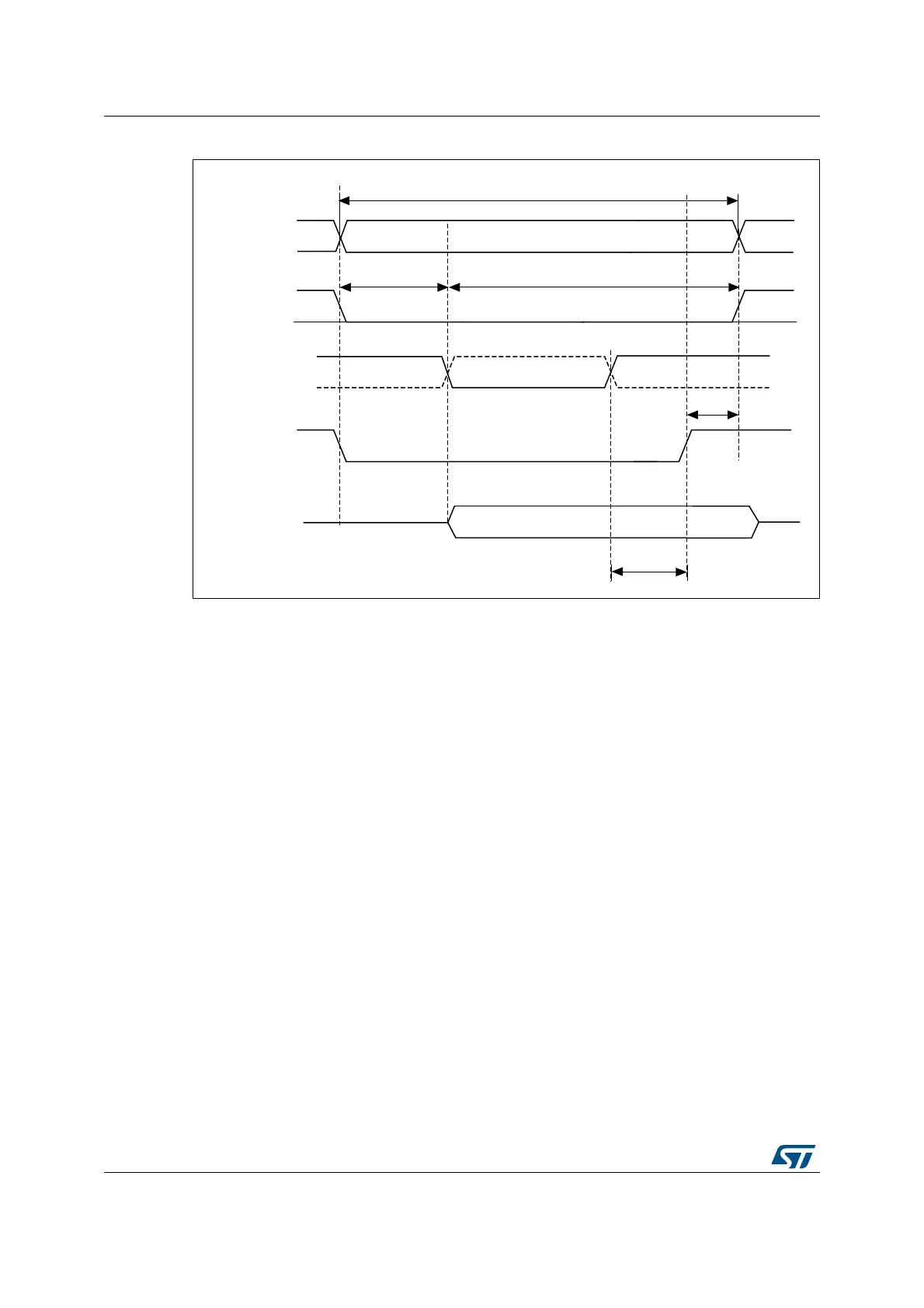

NOR Flash memories specify a minimum time from NADV assertion to CLK high. To meet

this constraint, the FMC does not issue the clock to the memory during the first internal

clock cycle of the synchronous access (before NADV assertion). This guarantees that the

rising edge of the memory clock occurs in the middle of the NADV low pulse.

Data latency versus NOR memory latency

The data latency is the number of cycles to wait before sampling the data. The DATLAT

value must be consistent with the latency value specified in the NOR Flash configuration

register. The FMC does not include the clock cycle when NADV is low in the data latency

count.

06Y9

$>@

1:(

0HPRU\WUDQVDFWLRQ

'>@

1([

GDWDGULYHQE\)0&

+&/.

DGGUHVVSKDVH

GDWDVHWXSSKDVH

+&/.

1:$,7

GRQ¶WFDUH GRQ¶WFDUH

FMC_CLK divider ratio max CLKDIV 1+ MWID AHB data size()(, )=

Loading...

Loading...