SD/SDIO/MMC card host interface (SDMMC) RM0351

1532/1830 DocID024597 Rev 5

• Receive FIFO

When the data path subunit receives a word of data, it drives the data on the write

databus. The write pointer is incremented after the write operation completes. On the

read side, the contents of the FIFO word pointed to by the current value of the read

pointer is driven onto the read databus. If the receive FIFO is disabled, all status flags

are deasserted, and the read and write pointers are reset. The data path subunit

asserts RXACT when it receives data. Table 272 lists the receive FIFO status flags.

The receive FIFO is accessible via 32 sequential addresses.

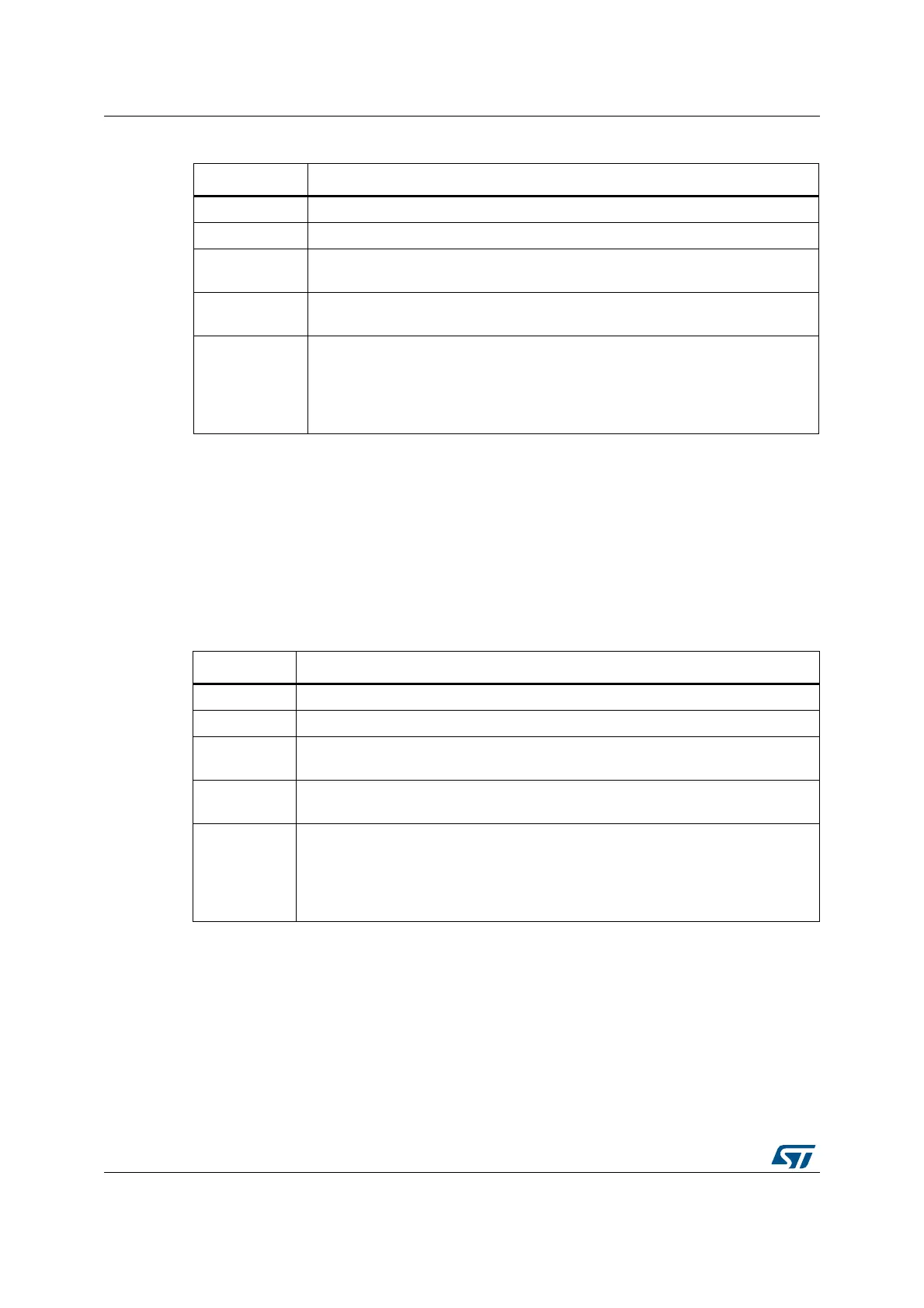

Table 271. Transmit FIFO status flags

Flag Description

TXFIFOF Set to high when all 32 transmit FIFO words contain valid data.

TXFIFOE Set to high when the transmit FIFO does not contain valid data.

TXFIFOHE

Set to high when 8 or more transmit FIFO words are empty. This flag can be used

as a DMA request.

TXDAVL

Set to high when the transmit FIFO contains valid data. This flag is the inverse of

the TXFIFOE flag.

TXUNDERR

Set to high when an underrun error occurs. This flag is cleared by writing to the

SDMMC Clear register.

Note: In case of TXUNDERR, and DMA is used to fill SDMMC FIFO, user

software should disable DMA stream, and then write DMAEN bit in

SDMMC_DCTRL with ‘0’ (to disable DMA request generation).

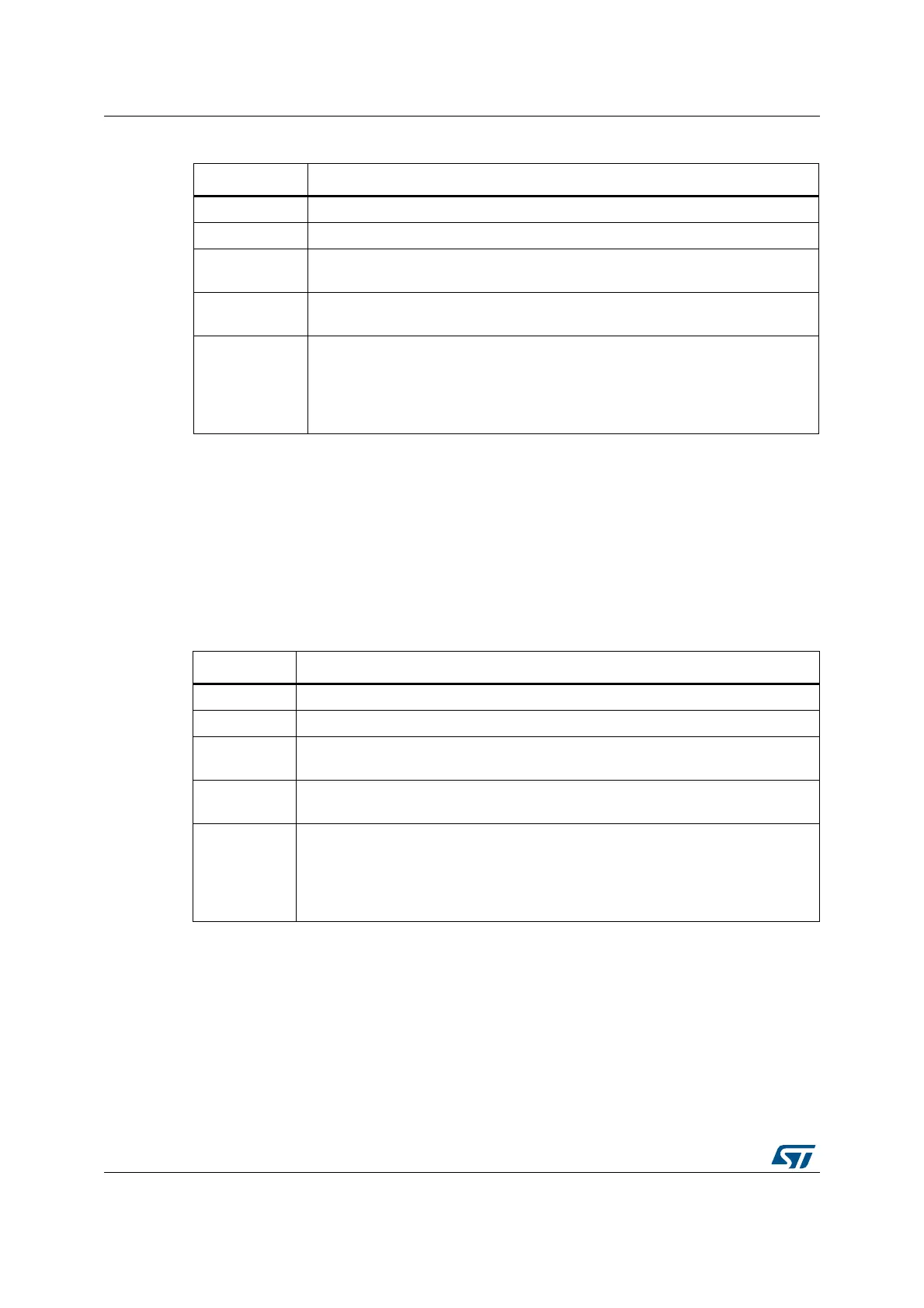

Table 272. Receive FIFO status flags

Flag Description

RXFIFOF Set to high when all 32 receive FIFO words contain valid data

RXFIFOE Set to high when the receive FIFO does not contain valid data.

RXFIFOHF

Set to high when 8 or more receive FIFO words contain valid data. This flag can be

used as a DMA request.

RXDAVL

Set to high when the receive FIFO is not empty. This flag is the inverse of the

RXFIFOE flag.

RXOVERR

Set to high when an overrun error occurs. This flag is cleared by writing to the

SDMMC Clear register.

Note: In case of RXOVERR, and DMA is used to read SDMMC FIFO, user

software should disable DMA stream, and then write DMAEN bit in

SDMMC_DCTRL with ‘0’ (to disable DMA request generation).

Loading...

Loading...