DocID024597 Rev 5 447/1830

RM0351 Flexible static memory controller (FSMC)

471

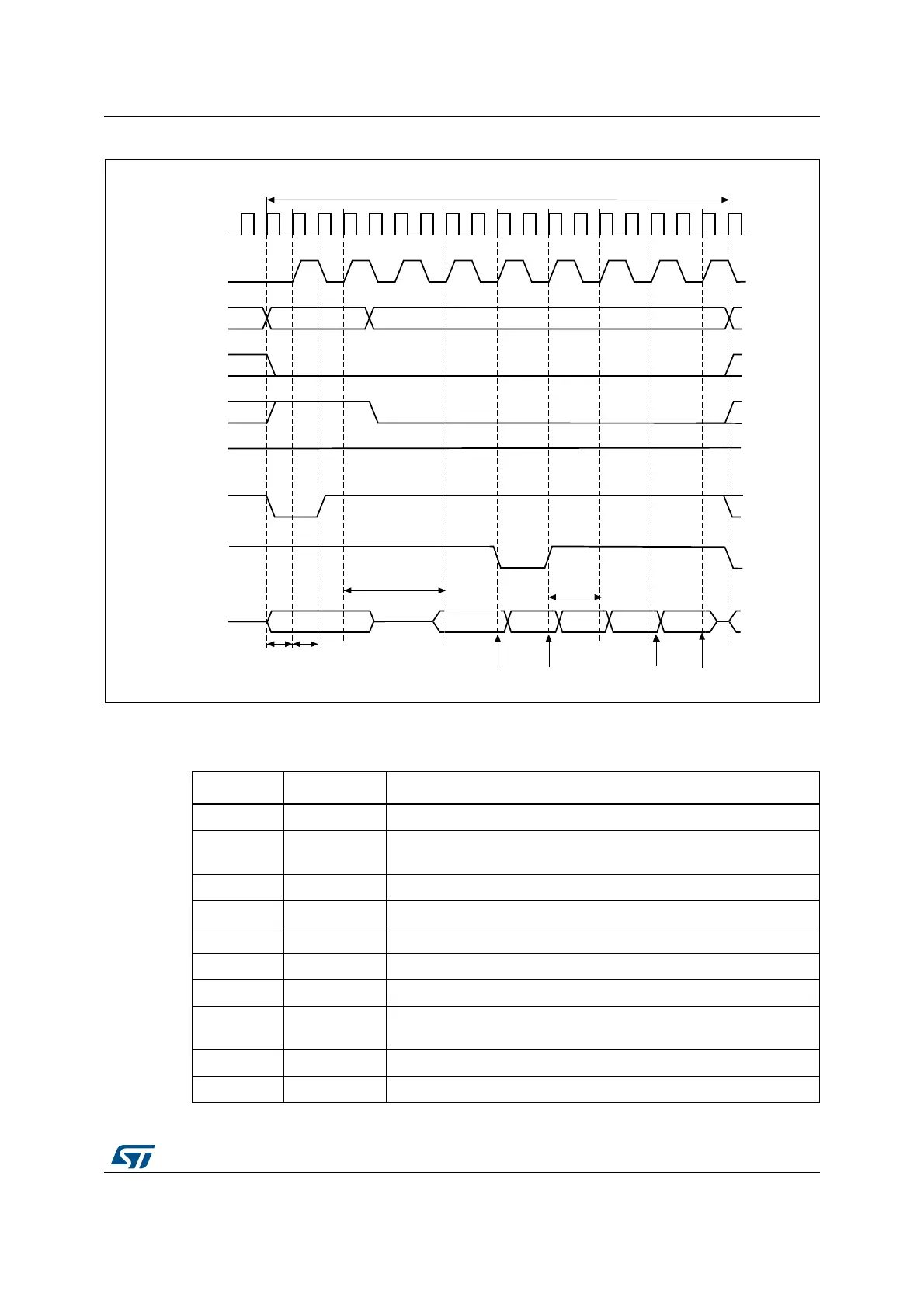

Figure 54. Synchronous multiplexed read mode waveforms - NOR, PSRAM (CRAM)

1. Byte lane outputs (NBL are not shown; for NOR access, they are held high, and, for PSRAM (CRAM)

access, they are held low.

$GGU>@ GDWD GDWD

DGGU>@

0HPRU\WUDQVDFWLRQ EXUVWRIKDOIZRUGV

+&/.

&/.

$>@

1([

12(

1:(

+LJK

1$'9

1:$,7

:$,7&)*

$'>@

FORFN

F\FOH

FORFN

F\FOH

'$7/$7

LQVHUWHGZDLWVWDWH

'DWDVWUREHV

DLI

&/.F\FOHV

GDWD GDWD

'DWDVWUREHV

Table 88. FMC_BCRx bit fields

Bit number Bit name Value to set

31-22 Reserved 0x000

21 WFDIS

As needed (this bit is reserved for STM32L475xx/476xx/486xx

devices)

20 CCLKEN As needed

19 CBURSTRW No effect on synchronous read

18:16 CPSIZE 0x0 (no effect in asynchronous mode)

15 ASYNCWAIT 0x0

14 EXTMOD 0x0

13 WAITEN

To be set to 1 if the memory supports this feature, to be kept at 0

otherwise

12 WREN No effect on synchronous read

11 WAITCFG To be set according to memory

Loading...

Loading...