Analog-to-digital converters (ADC) RM0351

554/1830 DocID024597 Rev 5

18.4.30 Oversampler

The oversampling unit performs data pre-processing to offload the CPU. It is able to handle

multiple conversions and average them into a single data with increased data width, up to

16-bit.

It provides a result with the following form, where N and M can be adjusted:

It allows to perform by hardware the following functions: averaging, data rate reduction,

SNR improvement, basic filtering.

The oversampling ratio N is defined using the OVFS[2:0] bits in the ADC_CFGR2 register,

and can range from 2x to 256x. The division coefficient M consists of a right bit shift up to

8 bits, and is defined using the OVSS[3:0] bits in the ADC_CFGR2 register.

The summation unit can yield a result up to 20 bits (256x 12-bit results), which is first shifted

right. It is then truncated to the 16 least significant bits, rounded to the nearest value using

the least significant bits left apart by the shifting, before being finally transferred into the

ADC_DR data register.

Note: If the intermediary result after the shifting exceeds 16-bit, the result is truncated as is,

without saturation.

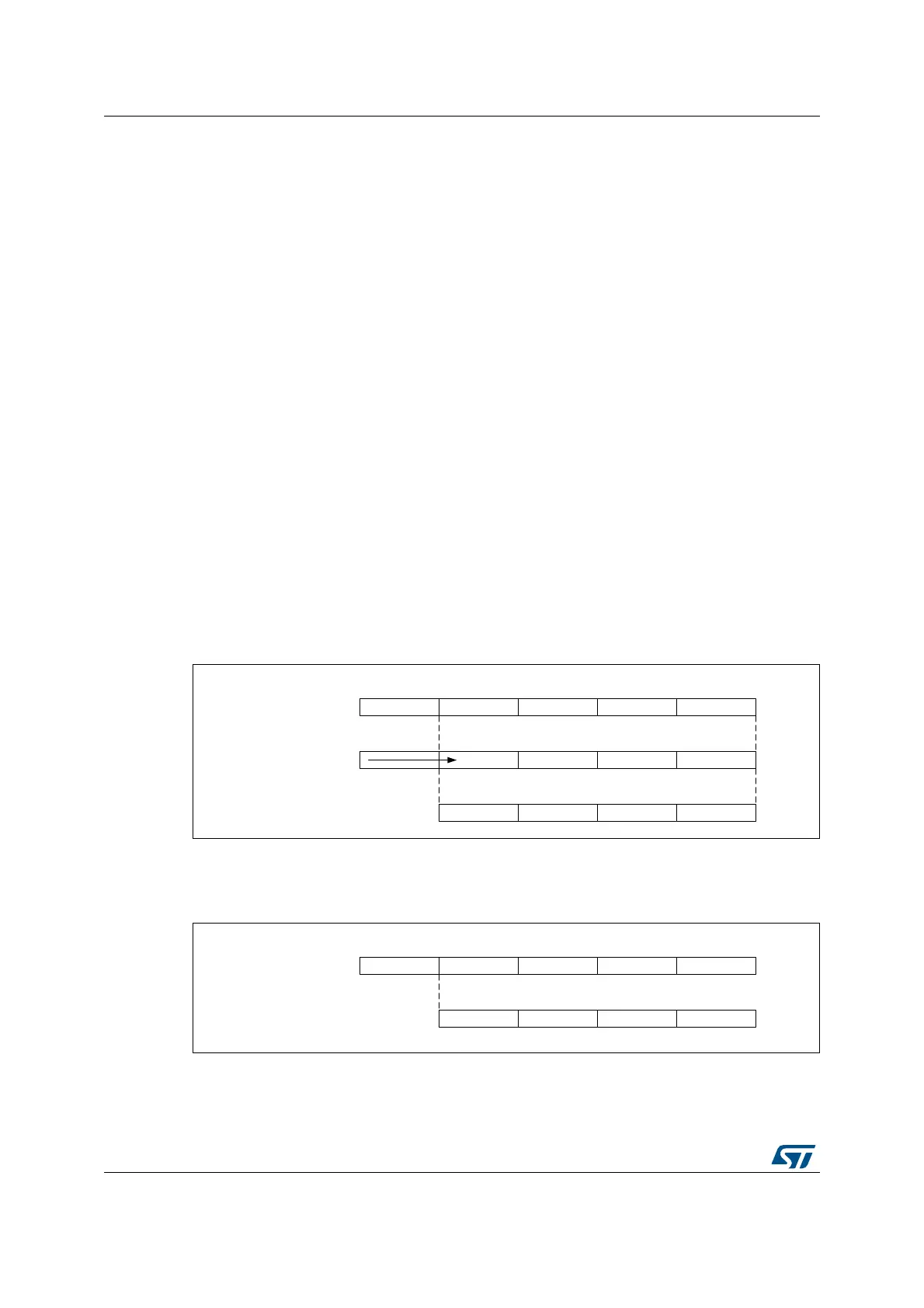

Figure 111. 20-bit to 16-bit result truncation

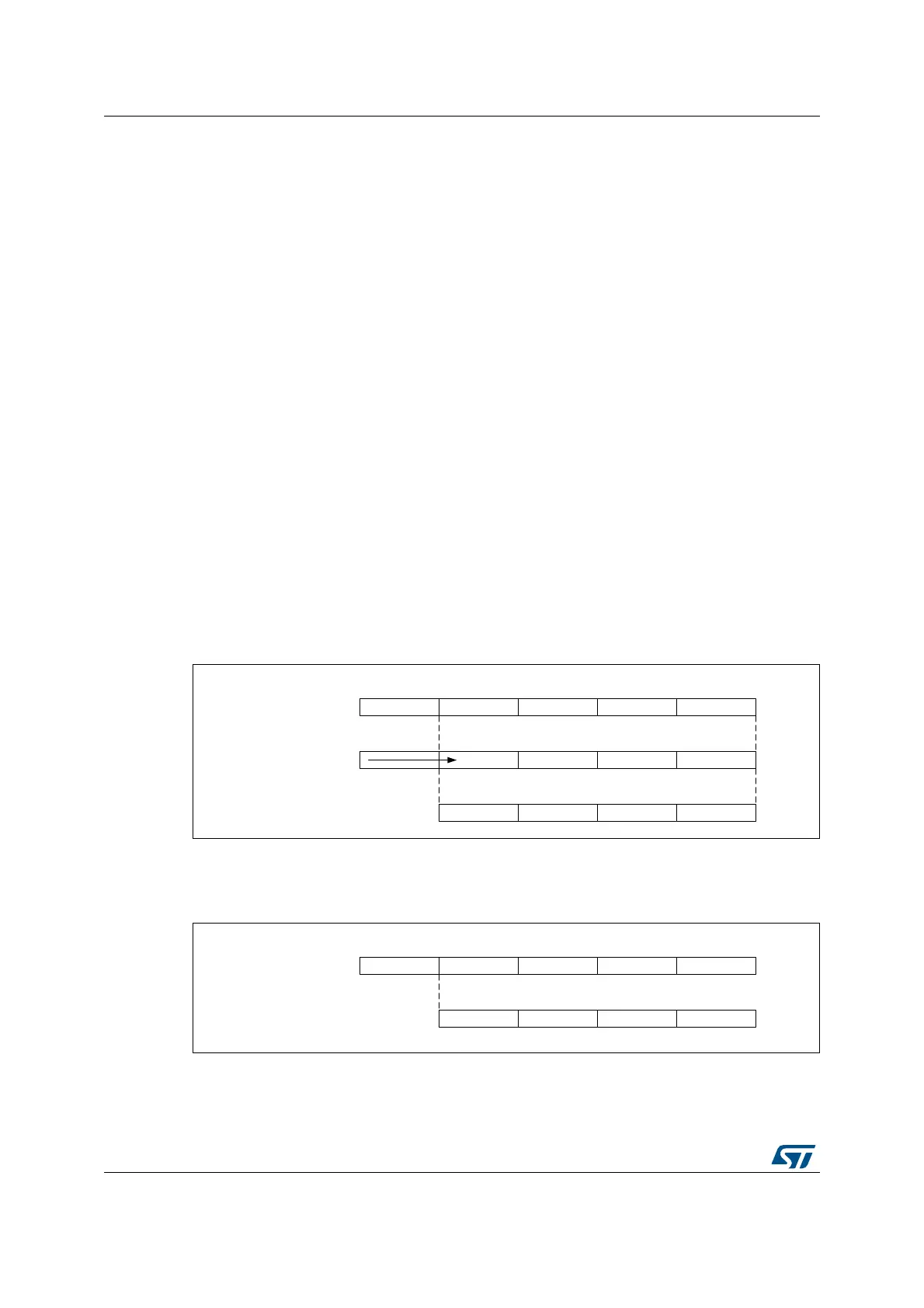

The Figure 112 gives a numerical example of the processing, from a raw 20-bit accumulated

data to the final 16-bit result.

Figure 112. Numerical example with 5-bits shift and rounding

The Table 114 below gives the data format for the various N and M combinations, for a raw

conversion data equal to 0xFFF.

Result

1

M

---- -

Conversion t

n

()

n0=

nN1–=

∑

×=

069

5DZELWGDWD

6KLIWLQJ

7UXQFDWLRQDQGURXQGLQJ

069

'5DZELWGDWD

)%'

)LQDOUHVXOWDIWHUELWVKLIW

DQGURXQGLQJWRQHDUHVW

%

Loading...

Loading...