SD/SDIO/MMC card host interface (SDMMC) RM0351

1520/1830 DocID024597 Rev 5

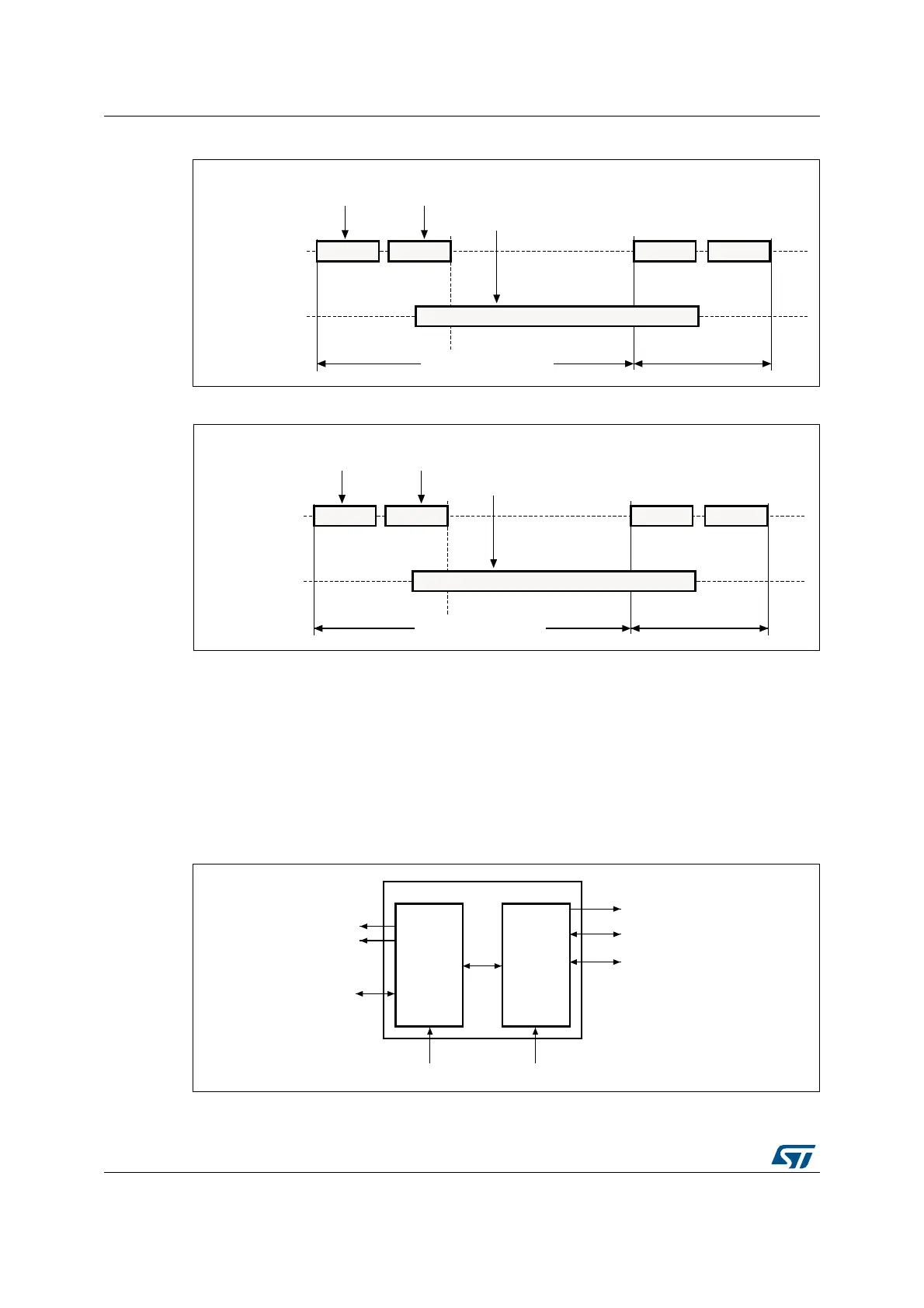

Figure 490. Sequential read operation

Figure 491. Sequential write operation

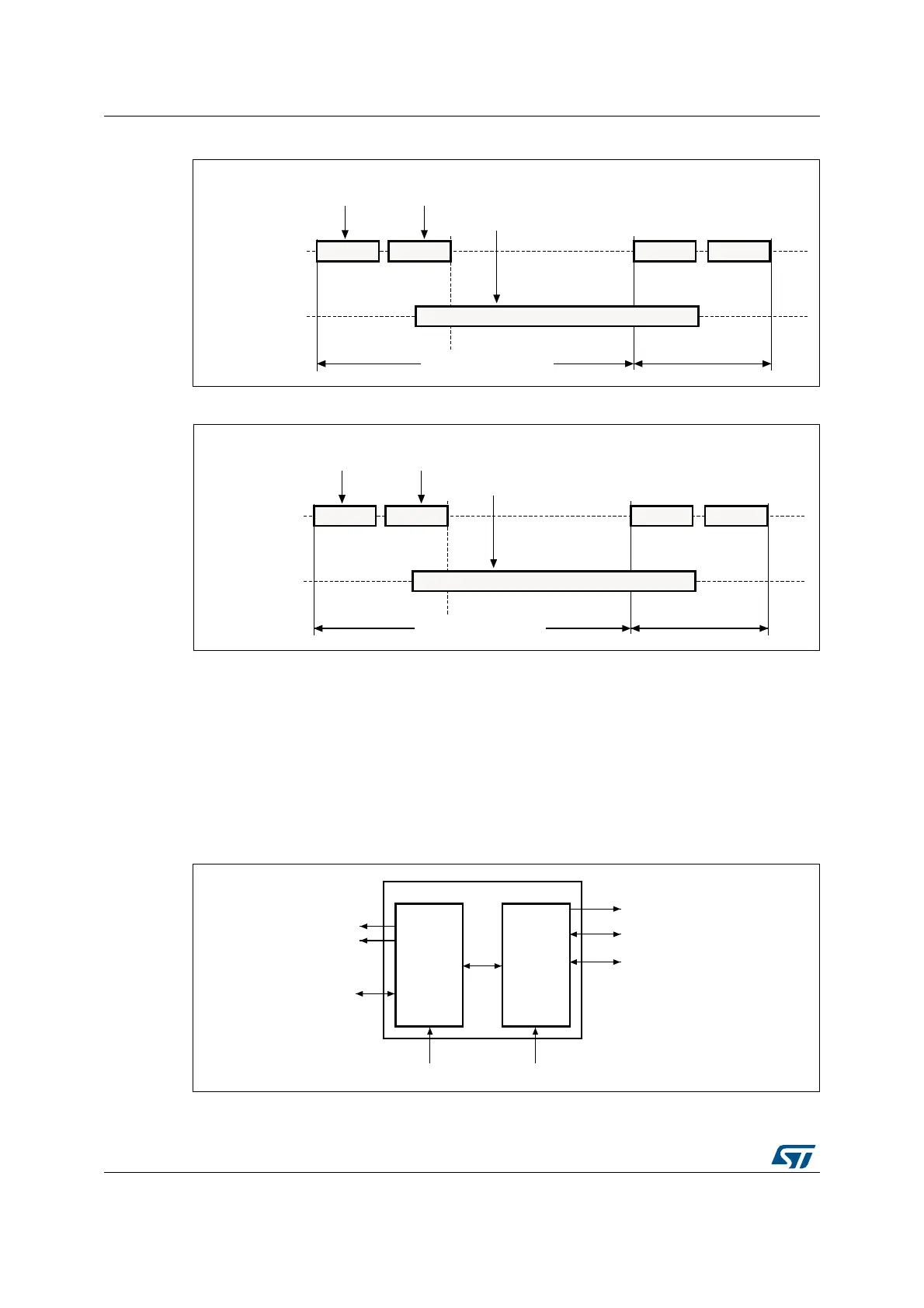

45.3 SDMMC functional description

The SDMMC consists of two parts:

• The SDMMC adapter block provides all functions specific to the MMC/SD/SD I/O card

such as the clock generation unit, command and data transfer.

• The APB2 interface accesses the SDMMC adapter registers, and generates interrupt

and DMA request signals.

Figure 492. SDMMC block diagram

DLE

'DWDVWRSRSHUDWLRQ

)URPFDUGWRKRVW

6WRSFRPPDQG

VWRSVGDWDWUDQVIHU

&RPPDQG 5HVSRQVH &RPPDQG 5HVSRQVH

'DWDVWUHDP

'DWDWUDQVIHURSHUDWLRQ

)URPKRVWWR

FDUGV

'DWDIURPFDUGWRKRVW

6'00&B&0'

6'00&B'

DLE

'DWDVWRSRSHUDWLRQ

)URPFDUGWRKRVW

6WRSFRPPDQG

VWRSVGDWDWUDQVIHU

5HVSRQVH&RPPDQG 5HVSRQVH&RPPDQG

'DWDVWUHDP

'DWDWUDQVIHURSHUDWLRQ

)URPKRVWWR

FDUGV

'DWDIURPKRVWWRFDUG

6'00&B&0'

6'00&B'

DLE

$3%EXV

$3%

,QWHUUXSWVDQG

3&/.

6'00&B&.

LQWHUIDFH

'0$UHTXHVW

6'00&&/.

6'00&B'>@

6'00&B&0'

6'00&

6'00&

DGDSWHU

Loading...

Loading...