Analog-to-digital converters (ADC) RM0351

570/1830 DocID024597 Rev 5

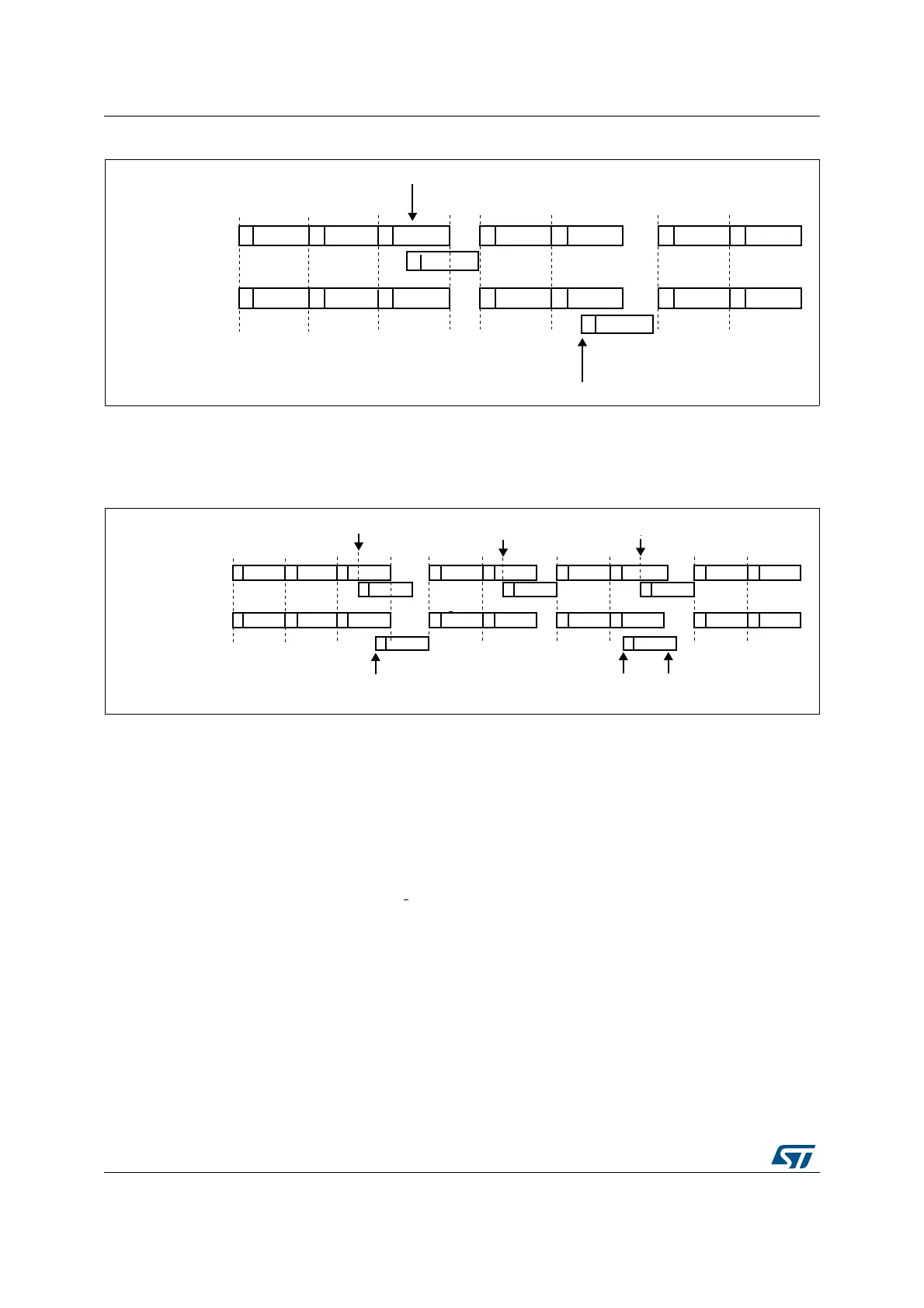

Figure 126. Alternate + regular simultaneous

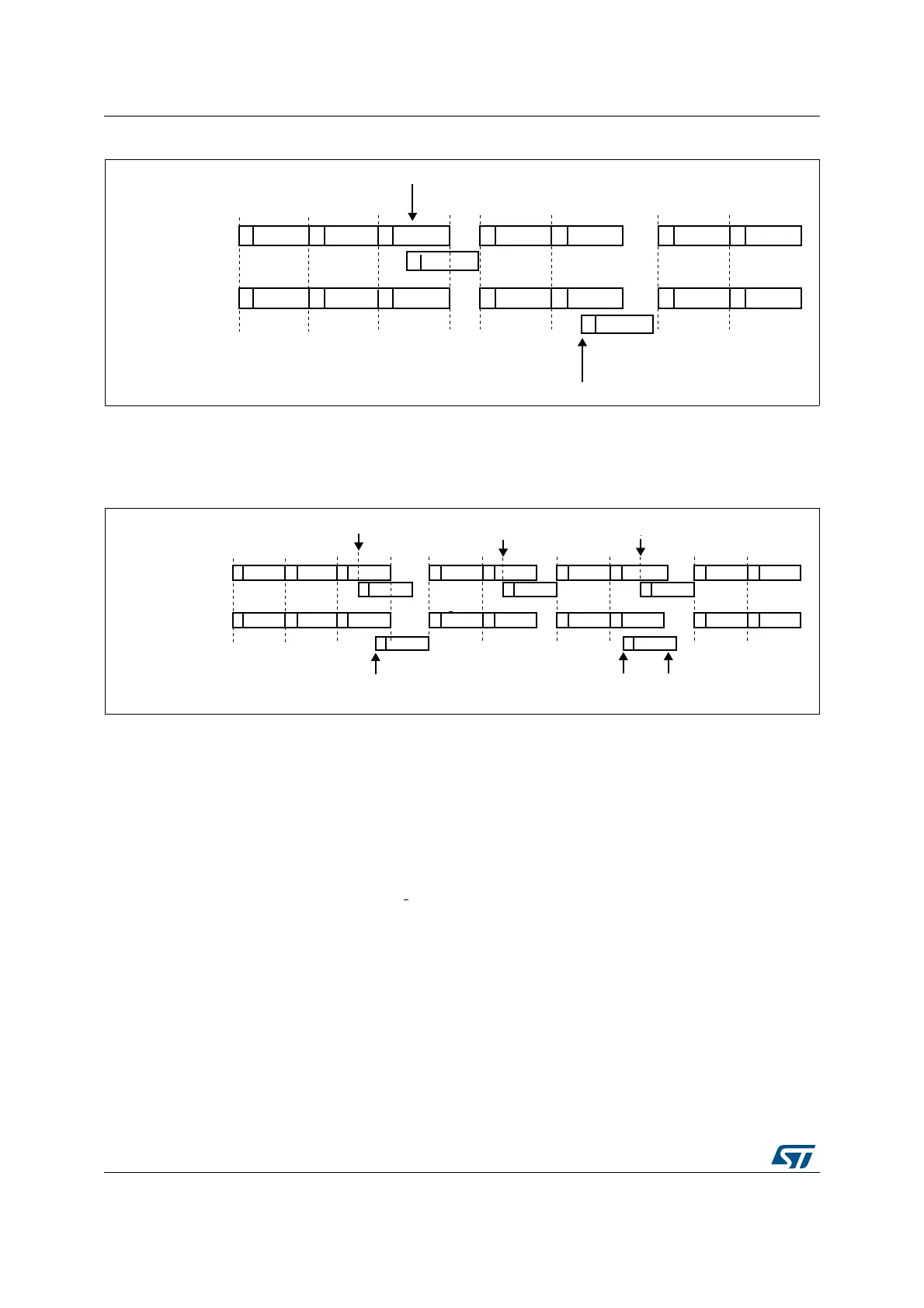

If a trigger occurs during an injected conversion that has interrupted a regular conversion,

the alternate trigger is served. Figure 127 shows the behavior in this case (note that the 6th

trigger is ignored because the associated alternate conversion is not complete).

Figure 127. Case of trigger occurring during injected conversion

Combined injected simultaneous plus interleaved

This mode is selected by programming bits DUAL[4:0]=00011

It is possible to interrupt an interleaved conversion with a simultaneous injected event.

In this case the interleaved conversion is interrupted immediately and the simultaneous

injected conversion starts. At the end of the injected sequence the interleaved conversion is

resumed. When the interleaved regular conversion resumes, the first regular conversion

which is performed is alway the master’s one. Figure 128, Figure 129 and Figure 130 show

the behavior using an example.

Caution: In this mode, it is mandatory to use the Common Data Register to read the regular data with

a single read access. On the contrary, master-slave data coherency is not guaranteed.

$'&0$67(5UHJ

&+ &+ &+

&+

&+ &+

&+

$'&0$67(5LQM

$'&6/$9(UHJ

$'&6/$9(LQM

VWWULJJHU

QGWULJJHU

V\QFKURQRWORVW

&+ &+ &+ &+ &+

&+ &+

&+ &+

DL9P

$'&0$67(5UHJ

&+

&+

&+

$'&0$67(5LQM

$'&6/$9(UHJ

$'&6/$9(LQM

VWWULJJHU

QGWULJJHU

&+ &+

&+

&+

DL9

&+

WKWULJJHU

UGWULJJHU

&+

&+

WKWULJJHU

&+

WKWULJJHU

LJQRUHG

&+

&+

&+

&+

&+ &+ &+

&+ &+ &+

&+

&+

Loading...

Loading...