USB on-the-go full-speed (OTG_FS) RM0351

1656/1830 DocID024597 Rev 5

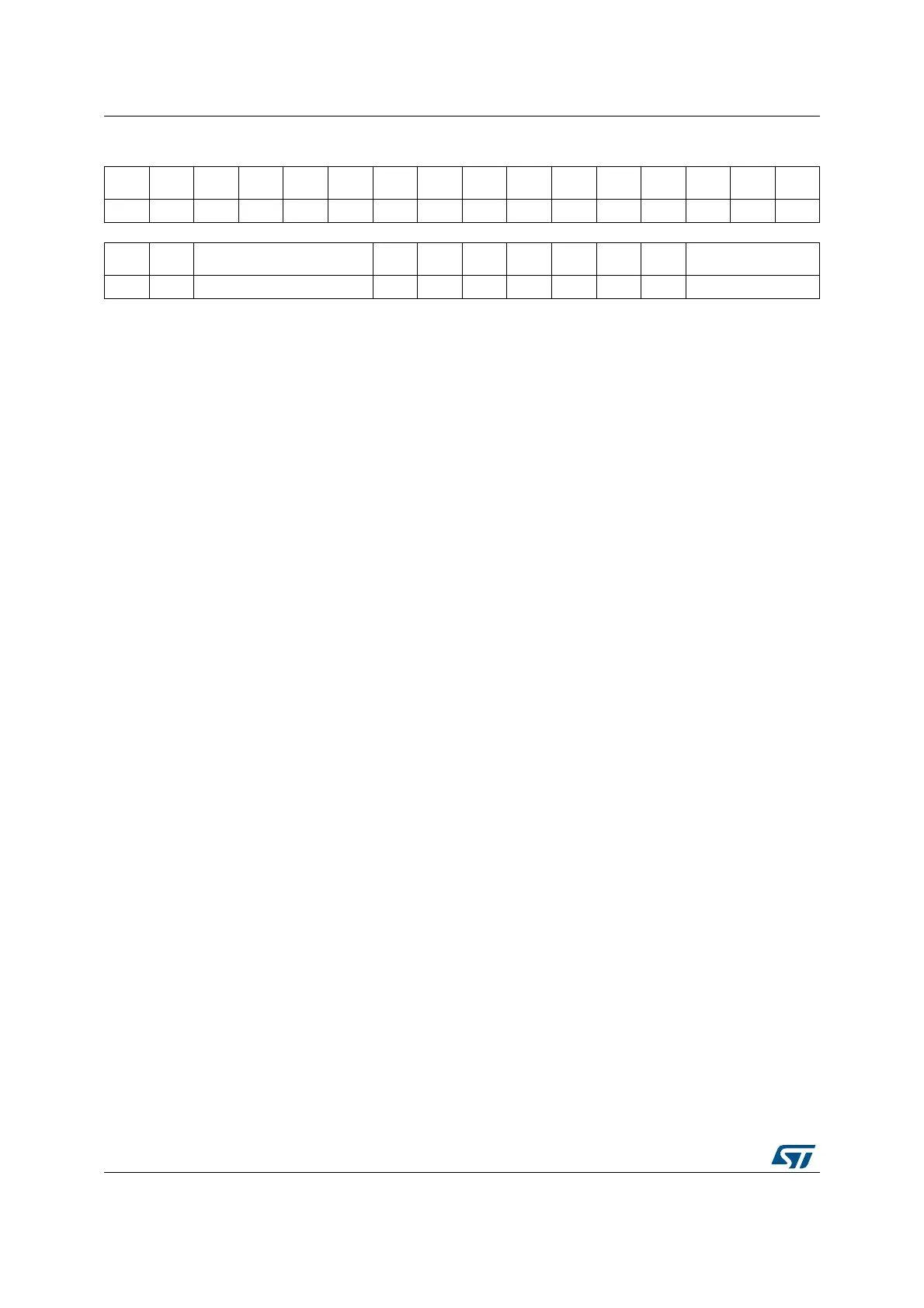

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

FD

MOD

FH

MOD

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw

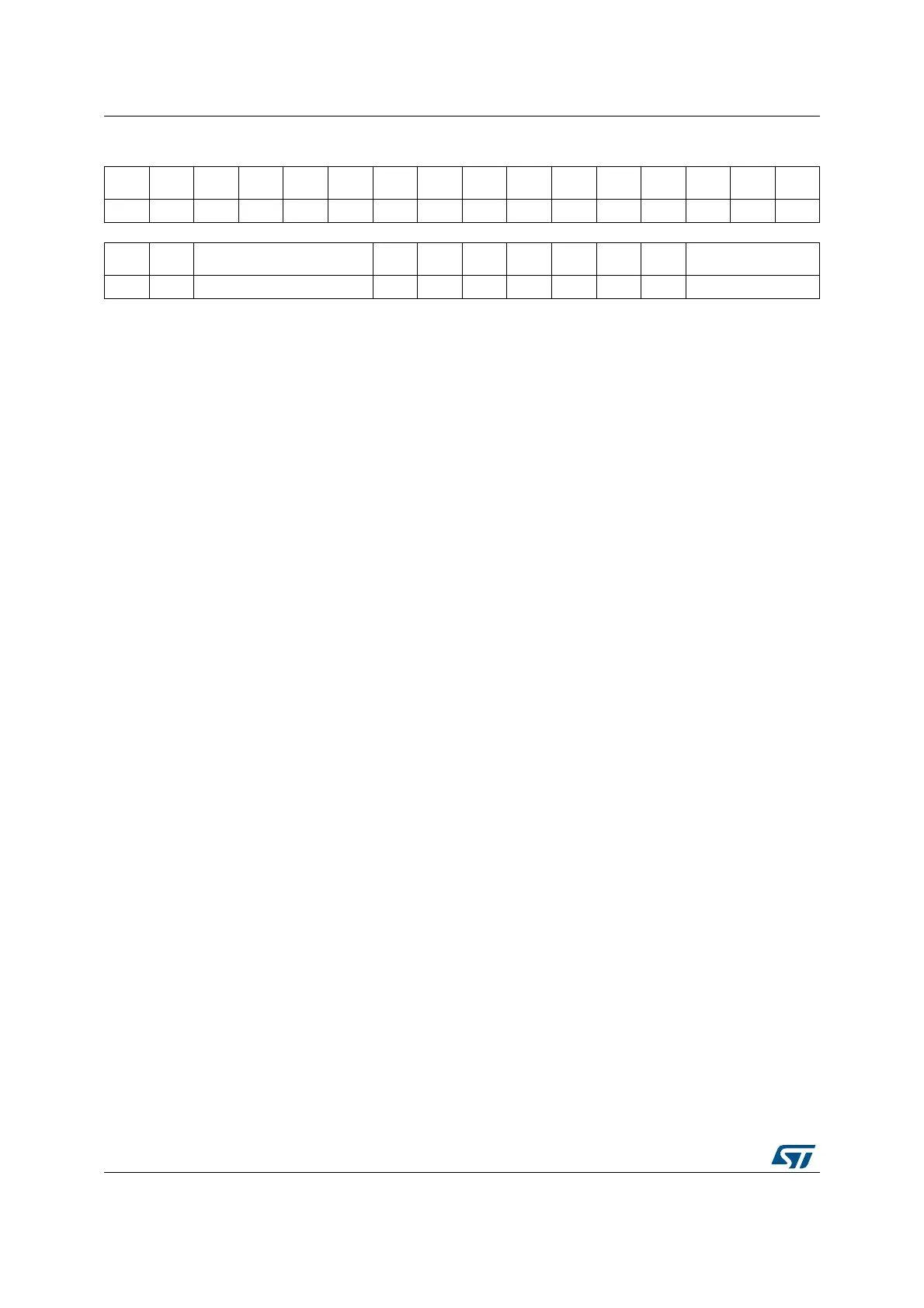

1514131211109876543210

Res. Res. TRDT

HNP

CAP

SRP

CAP

Res.

PHY

SEL

Res. Res. Res. TOCAL

rw rw rw r rw

Bit 31 Reserved, must be kept at reset value.

Bit 30 FDMOD: Force device mode

Writing a 1 to this bit, forces the core to device mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force device mode

After setting the force bit, the application must wait at least 25 ms before the change takes

effect.

Note: Accessible in both device and host modes.

Bit 29 FHMOD: Force host mode

Writing a 1 to this bit, forces the core to host mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force host mode

After setting the force bit, the application must wait at least 25 ms before the change takes

effect.

Note: Accessible in both device and host modes.

Bits 28:26 Reserved, must be kept at reset value for USB OTG HS and FS

Bits 25:15 Reserved, must be kept at reset value for USB OTG FS

Bit 14 Reserved, must be kept at reset value.

Bits 13:10 TRDT: USB turnaround time

These bits allows to set the turnaround time in PHY clocks. They must be configured

according to Table 307: TRDT values(FS), depending on the application AHB frequency.

Higher TRDT values allow stretching the USB response time to IN tokens in order to

compensate for longer AHB read access latency to the Data FIFO.

Note: Only accessible in device mode.

Bit 9 HNPCAP: HNP-capable

The application uses this bit to control the

OTG_FS controller’s HNP capabilities.

0: HNP capability is not enabled.

1: HNP capability is enabled.

Note: Accessible in both device and host modes.

Bit 8 SRPCAP: SRP-capable

The application uses this bit to control the

OTG_FS controller’s SRP capabilities. If the core

operates as a non-SRP-capable

B-device, it cannot request the connected A-device (host) to activate V

BUS

and start a

session.

0: SRP capability is not enabled.

1: SRP capability is enabled.

Note: Accessible in both device and host modes.

Bit 7 Reserved, must be kept at reset value.

Loading...

Loading...