Low-power timer (LPTIM) RM0351

1166/1830 DocID024597 Rev 5

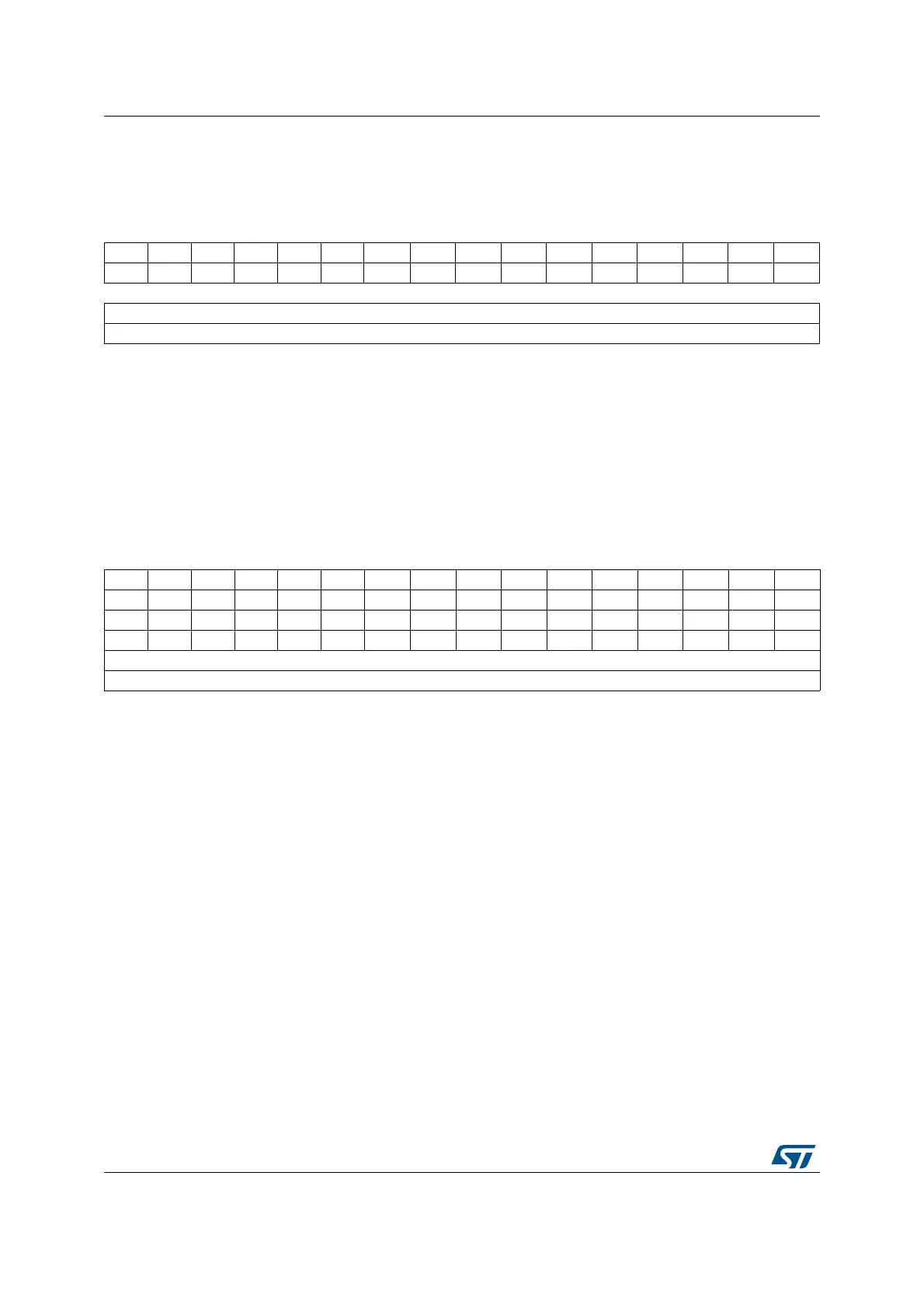

34.7.6 LPTIM compare register (LPTIM_CMP)

Address offset: 0x14

Reset value: 0x0000 0000

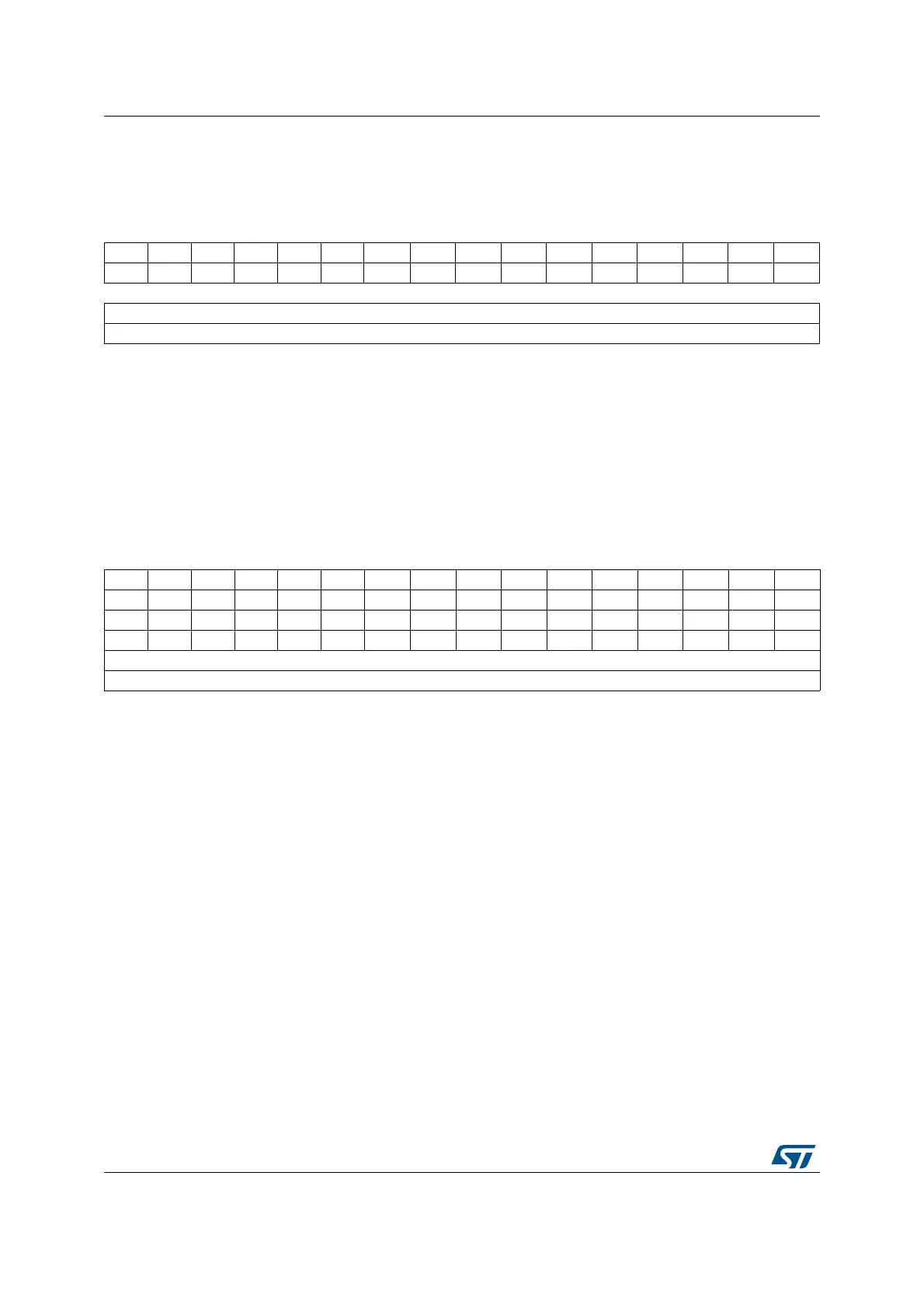

34.7.7 LPTIM autoreload register (LPTIM_ARR)

Address offset: 0x18

Reset value: 0x0000 0001

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CMP[15:0]

rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 CMP: Compare value

CMP is the compare value used by the LPTIM.

The LPTIM_CMP register’s content must only be modified when the LPTIM is enabled (ENABLE bit

is set to ‘1’).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ARR[15:0]

rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 ARR: Auto reload value

ARR is the autoreload value for the LPTIM.

This value must be strictly greater than the CMP[15:0] value.

The LPTIM_ARR register’s content must only be modified when the LPTIM is enabled (ENABLE bit

is set to ‘1’).

Loading...

Loading...