DocID024597 Rev 5 1221/1830

RM0351 Real-time clock (RTC)

1230

38.6.14 RTC time-stamp sub second register (RTC_TSSSR)

The content of this register is valid only when RTC_ISR/TSF is set. It is cleared when the

RTC_ISR/TSF bit is reset.

Address offset: 0x38

Backup domain reset value: 0x0000 0000

System reset: not affected

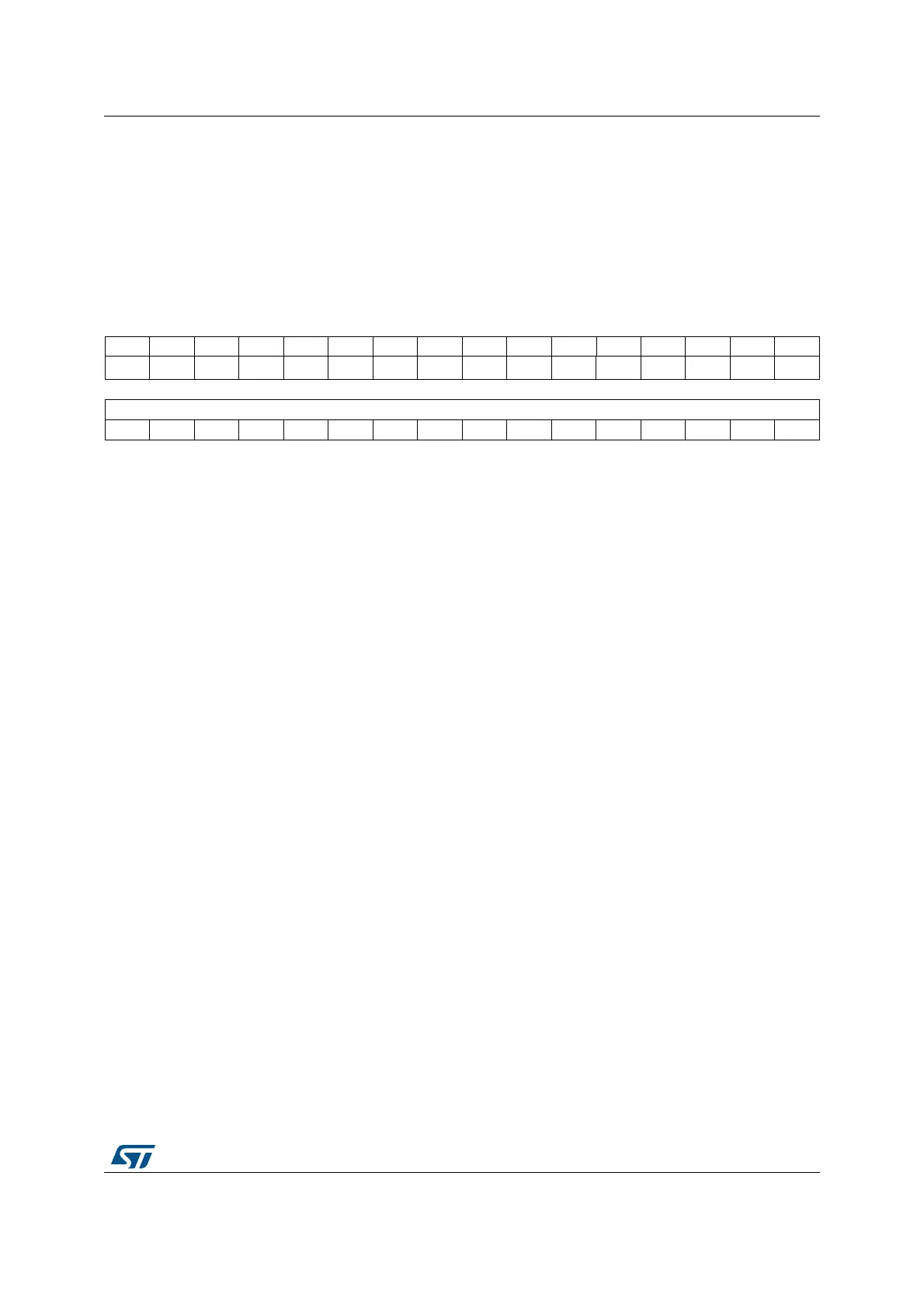

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

SS[15:0]

rrrrrrrrrrrrrrrr

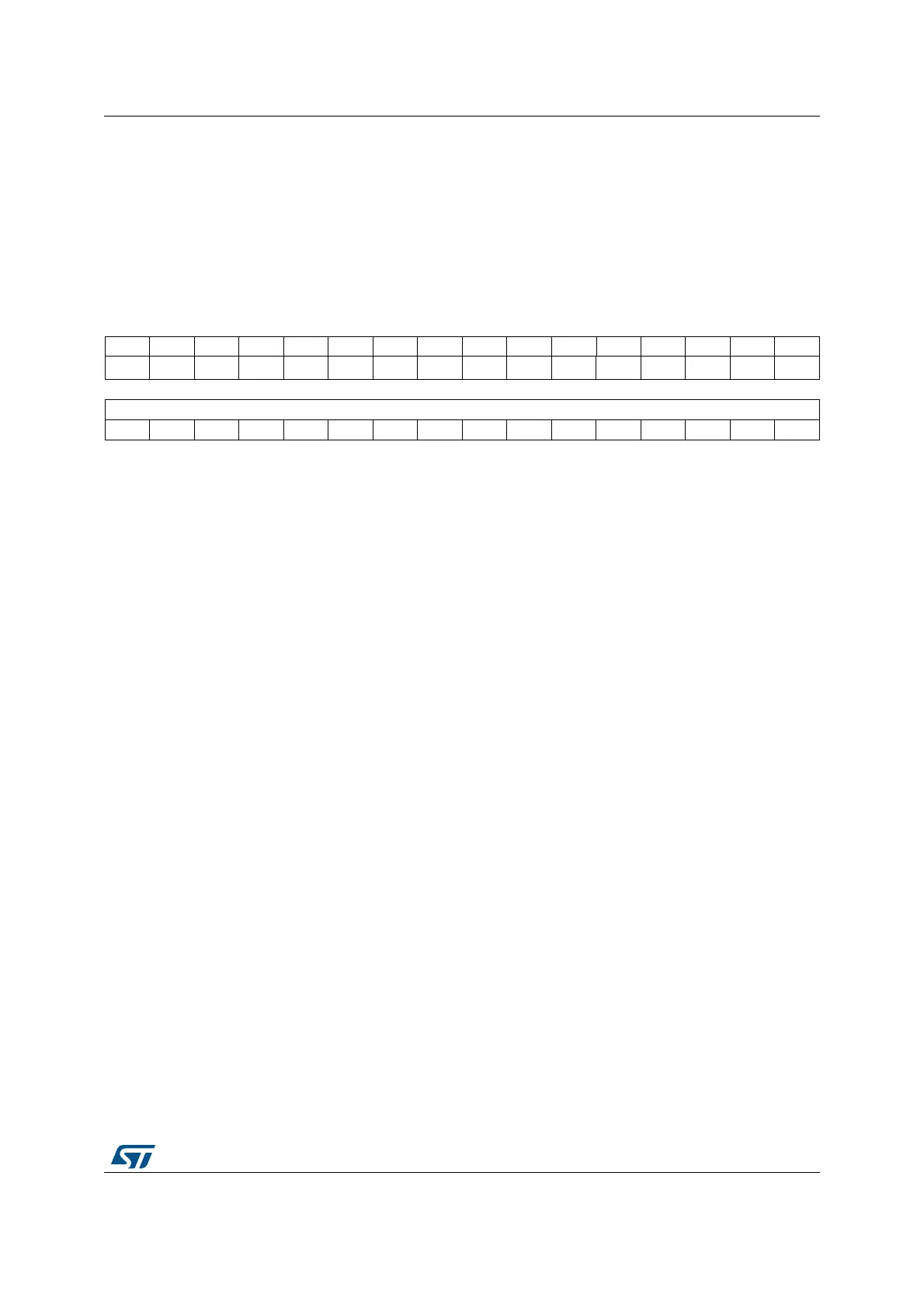

Bits 31:16 Reserved, must be kept at reset value

Bits 15:0 SS: Sub second value

SS[15:0] is the value of the synchronous prescaler counter when the timestamp event

occurred.

Loading...

Loading...