Reset and clock control (RCC) RM0351

244/1830 DocID024597 Rev 5

6.4.15 APB2 peripheral reset register (RCC_APB2RSTR)

Address offset: 0x40

Reset value: 0x00000 0000

Access: no wait state, word, half-word and byte access

Bit 2 SWPMI1RST: Single wire protocol reset

Set and cleared by software.

0: No effect

1: Reset SWPMI1

Bit 1 I2C4RST: I2C4 reset (This bit is reserved for STM32L475xx/476xx/486xx devices)

Set and cleared by software

0: No effect

1: Reset I2C4

Bit 0 LPUART1RST: Low-power UART 1 reset

Set and cleared by software.

0: No effect

1: Reset LPUART1

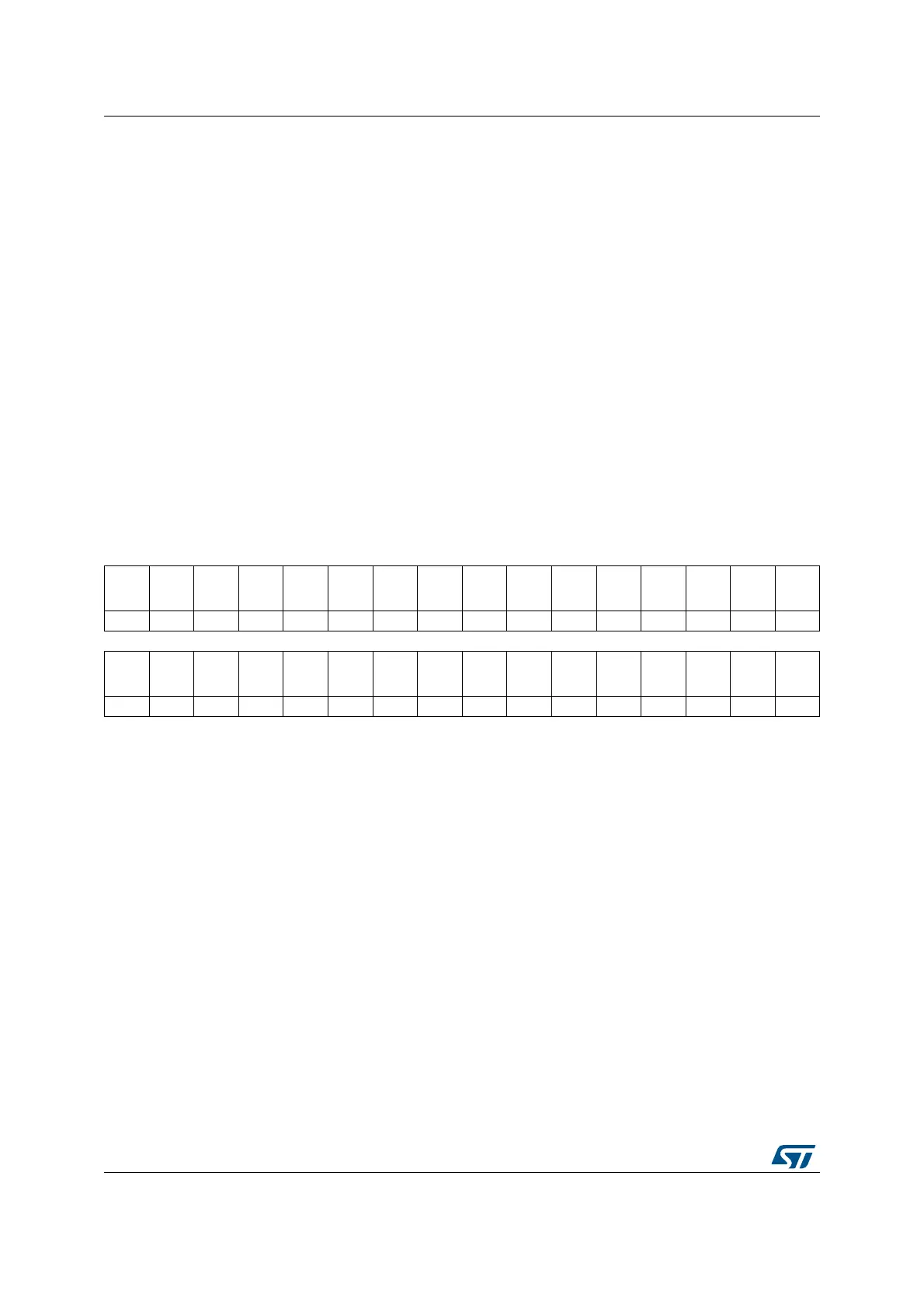

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res.

DFSD

M1

RST

Res.

SAI2

RST

SAI1

RST

Res. Res.

TIM17

RST

TIM16

RST

TIM15

RST

rw rw rw rw rw rw

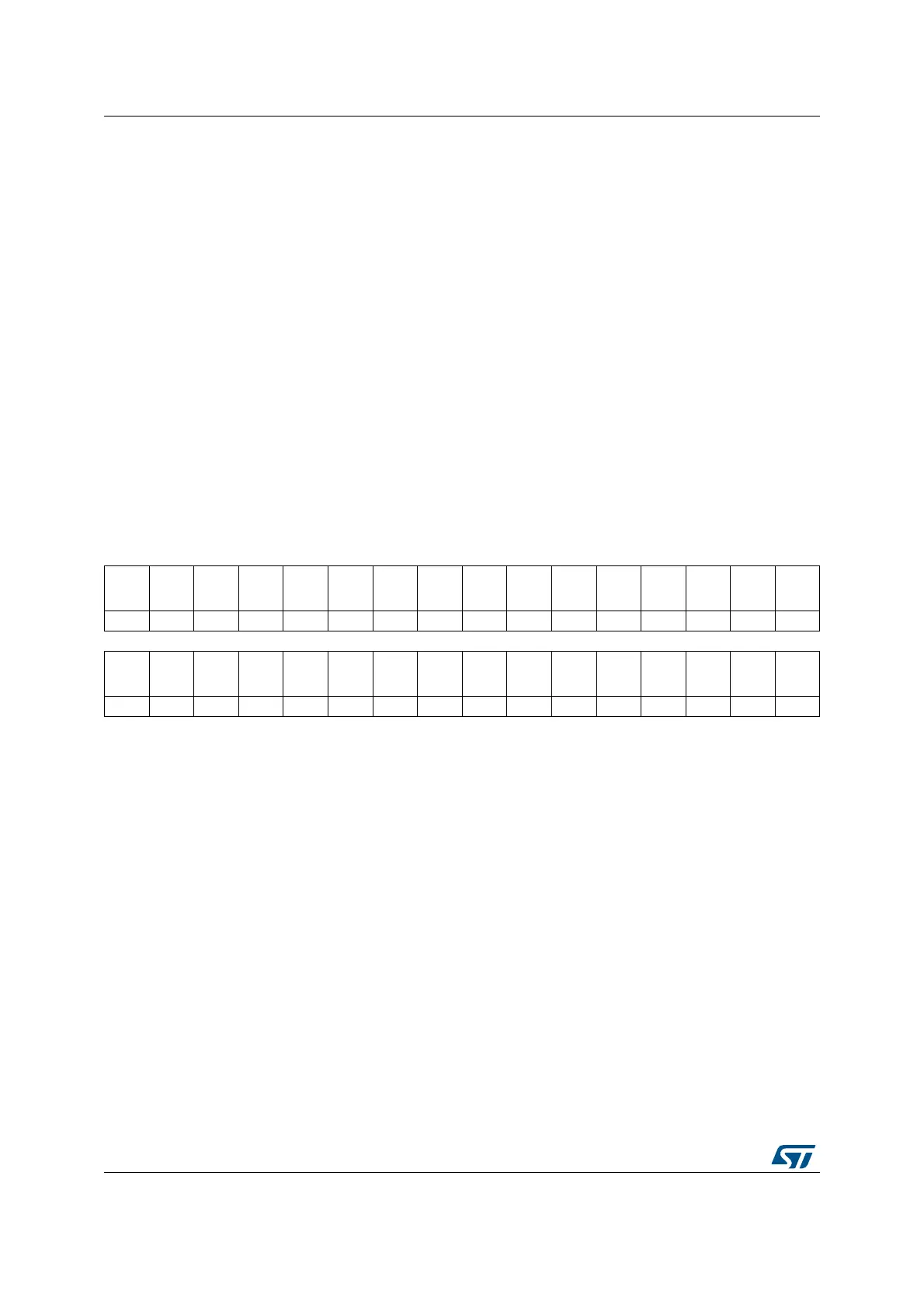

1514131211109876543210

Res.

USART

1

RST

TIM8

RST

SPI1

RST

TIM1

RST

SD

MMC1

RST

Res. Res. Res. Res. Res. Res. Res. Res. Res.

SYS

CFG

RST

rw rw rw rw rw rw

Bits 31:25 Reserved, must be kept at reset value.

Bit 24 DFSDM1RST: Digital filters for sigma-delta modulators (DFSDM1) reset

Set and cleared by software.

0: No effect

1: Reset DFSDM1

Bit 23 Reserved, must be kept at reset value.

Bit 22 SAI2RST: Serial audio interface 2 (SAI2) reset

Set and cleared by software.

0: No effect

1: Reset SAI2

Bit 21 SAI1RST: Serial audio interface 1 (SAI1) reset

Set and cleared by software.

0: No effect

1: Reset SAI1

Bits 20:19 Reserved, must be kept at reset value.

Loading...

Loading...