Reset and clock control (RCC) RM0351

246/1830 DocID024597 Rev 5

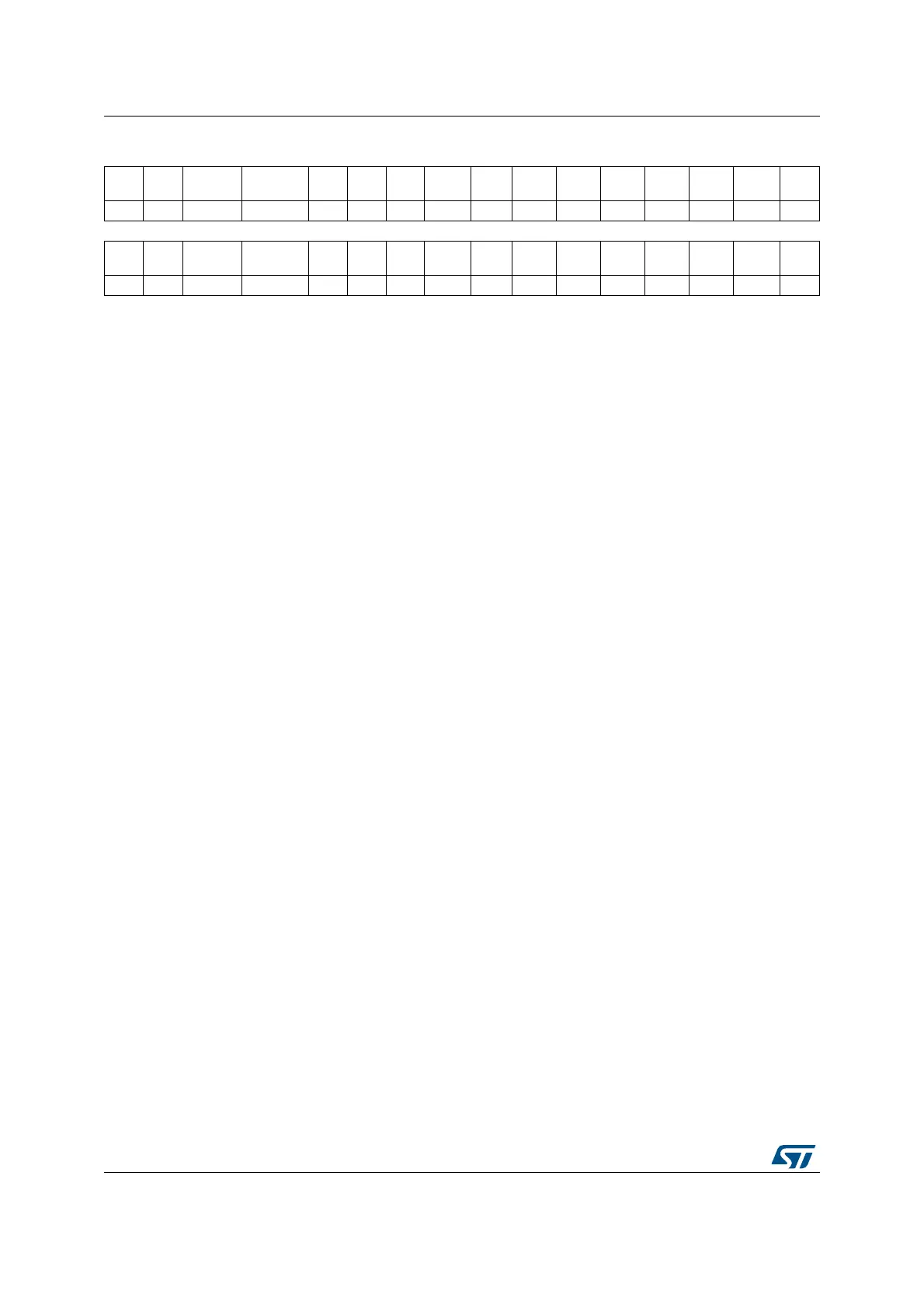

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DMA2D

EN

TSC

EN

rw rw

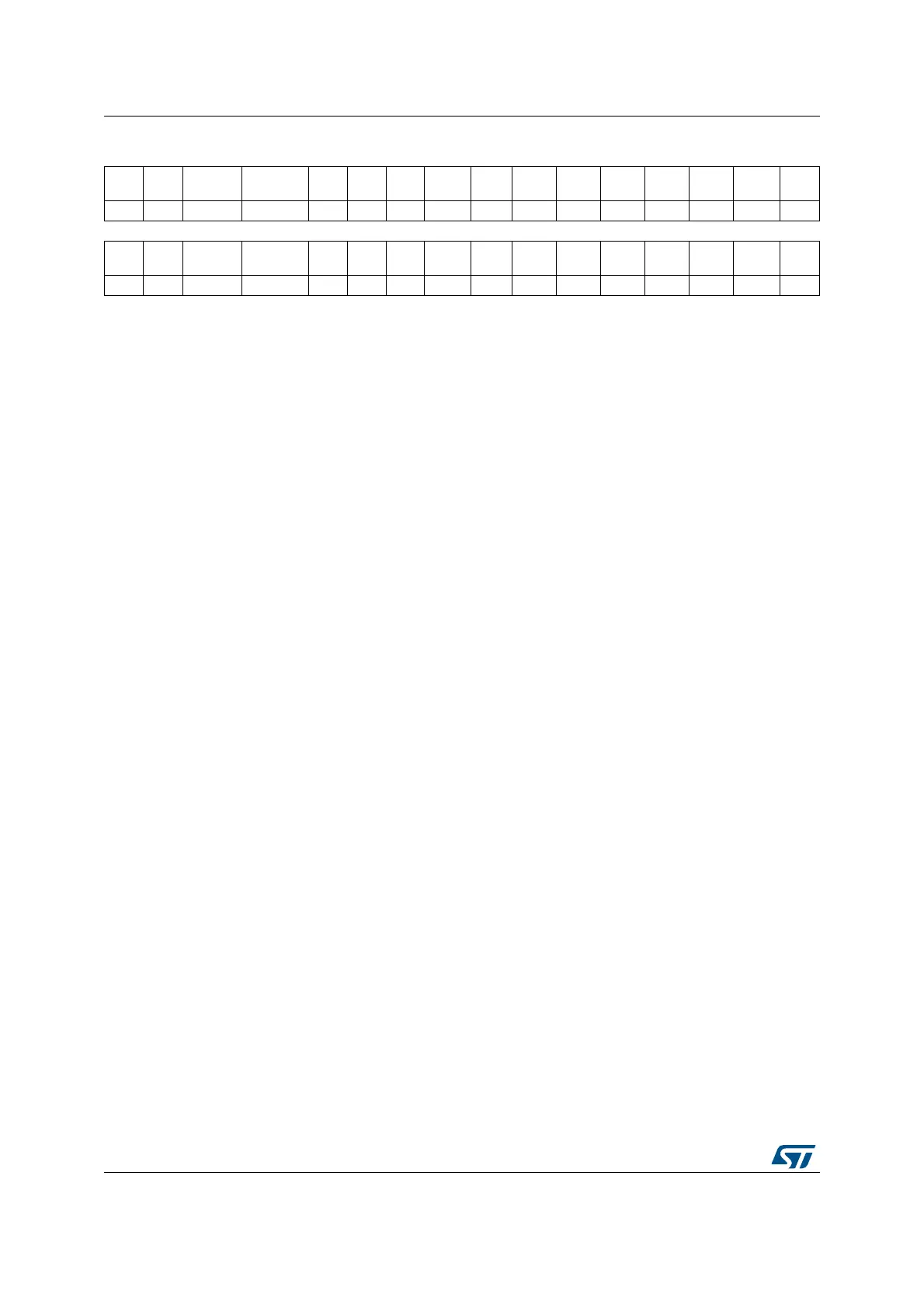

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. CRCEN Res. Res. Res.

FLASH

EN

Res. Res. Res. Res. Res. Res.

DMA2

EN

DMA1

EN

rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 DMA2DEN: DMA2D clock enable (This bit is reserved for STM32L475xx/476xx/486xx devices)

Set and cleared by software

0: DMA2D clock disabled

1: DMA2D clock enabled

Bit 16 TSCEN: Touch Sensing Controller clock enable

Set and cleared by software.

0: TSC clock disable

1: TSC clock enable

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 CRCEN: CRC clock enable

Set and cleared by software.

0: CRC clock disable

1: CRC clock enable

Bits 11:9 Reserved, must be kept at reset value.

Bit 8 FLASHEN: Flash memory interface clock enable

Set and cleared by software. This bit can be disabled only when the Flash is in power down

mode.

0: Flash memory interface clock disable

1: Flash memory interface clock enable

Bits 7:2 Reserved, must be kept at reset value.

Bit 1 DMA2EN: DMA2 clock enable

Set and cleared by software.

0: DMA2 clock disable

1: DMA2 clock enable

Bit 0 DMA1EN: DMA1 clock enable

Set and cleared by software.

0: DMA1 clock disable

1: DMA1 clock enable

Loading...

Loading...