DocID024597 Rev 5 349/1830

RM0351 Direct memory access controller (DMA)

356

11.5.6 DMA channel x memory address register (DMA_CMARx) (x = 1..7,

where x = channel number)

Address offset: 0x14 + 0d20 × (channel number – 1)

Reset value: 0x0000 0000

This register must not be written when the channel is enabled.

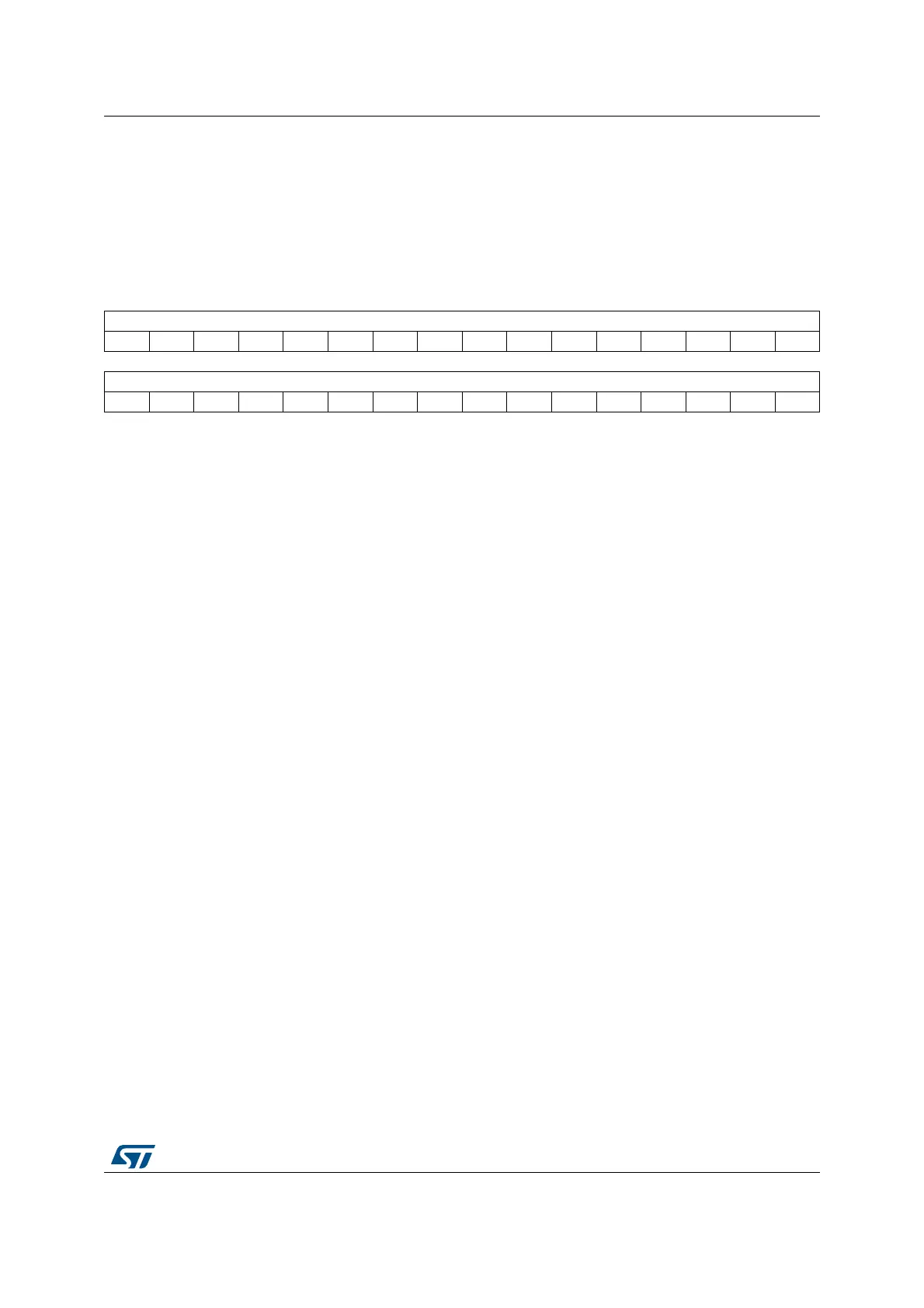

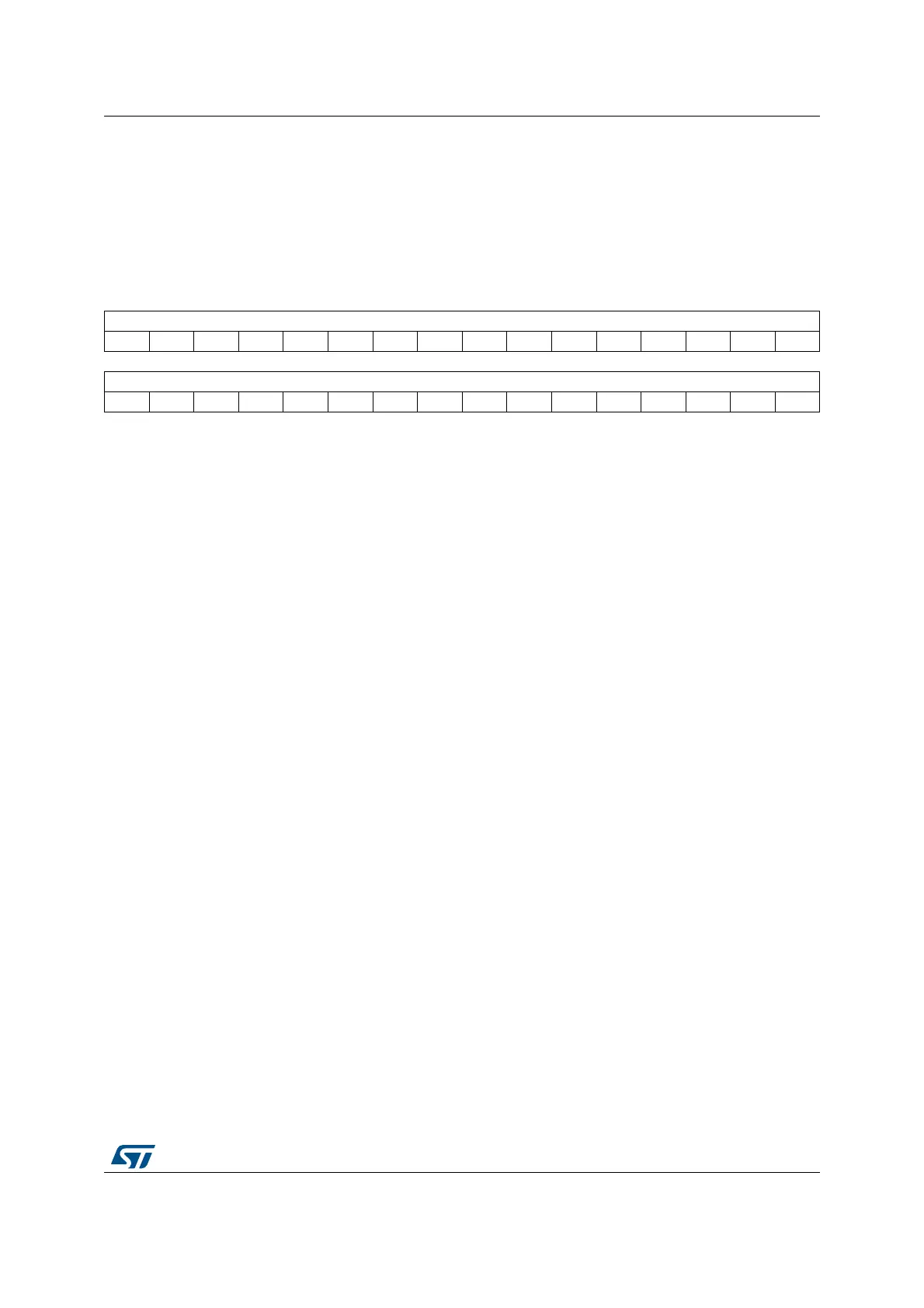

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

MA [31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

MA [15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 MA[31:0]: Memory address

Base address of the memory area from/to which the data will be read/written.

When MSIZE is 01 (16-bit), the MA[0] bit is ignored. Access is automatically aligned to a half-

word address.

When MSIZE is 10 (32-bit), MA[1:0] are ignored. Access is automatically aligned to a word

address.

Loading...

Loading...