DocID024597 Rev 5 471/1830

RM0351 Flexible static memory controller (FSMC)

471

Refer to Section 2.2.2 on page 75 for the register boundary addresses.

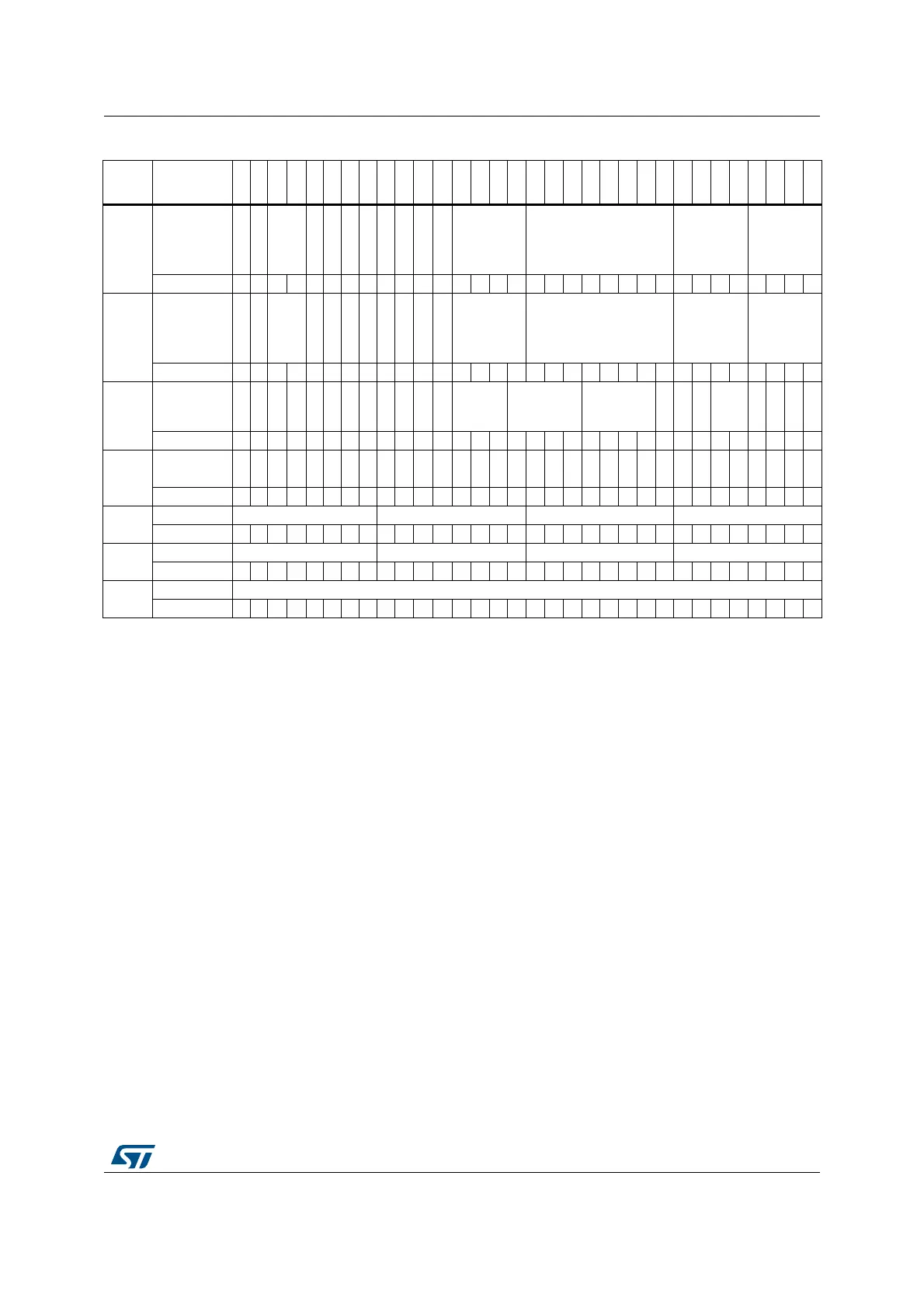

0x114

FMC_BWTR3

Res.

Res.

ACCMOD[1:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

BUSTURN[3:0] DATAST[7:0] ADDHLD[3:0] ADDSET[3:0]

Reset value 00 11111111111111111111

0x11C

FMC_BWTR4

Res.

Res.

ACCMOD[1:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

BUSTURN[3:0] DATAST[7:0] ADDHLD[3:0] ADDSET[3:0]

Reset value 00 11111111111111111111

0x80

FMC_PCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

ECCPS

[2:0]

TAR[3:0] TCLR[3:0]

Res.

Res.

ECCEN

PWID

[1:0]

PTYP

PBKEN

PWAITEN

Res.

Reset value 00000000000 001100

0x84

FMC_SR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

FEMPT

IFEN

ILEN

IREN

IFS

ILS

IRS

Reset value 1000000

0x88

FMC_PMEM MEMHIZx[7:0] MEMHOLDx[7:0] MEMWAITx[7:0] MEMSETx[7:0]

Reset value 11111100111 111001111110011111100

0x8C

FMC_PATT ATTHIZ[7:0] ATTHOLD[7:0] ATTWAIT[7:0] ATTSET[7:0]

Reset value 11111100111 111001111110011111100

0x94

FMC_ECCR ECCx[31:0]

Reset value 00000000000 000000000000000000000

1. This bit is reserved for STM32L475xx/476xx/486xx devices.

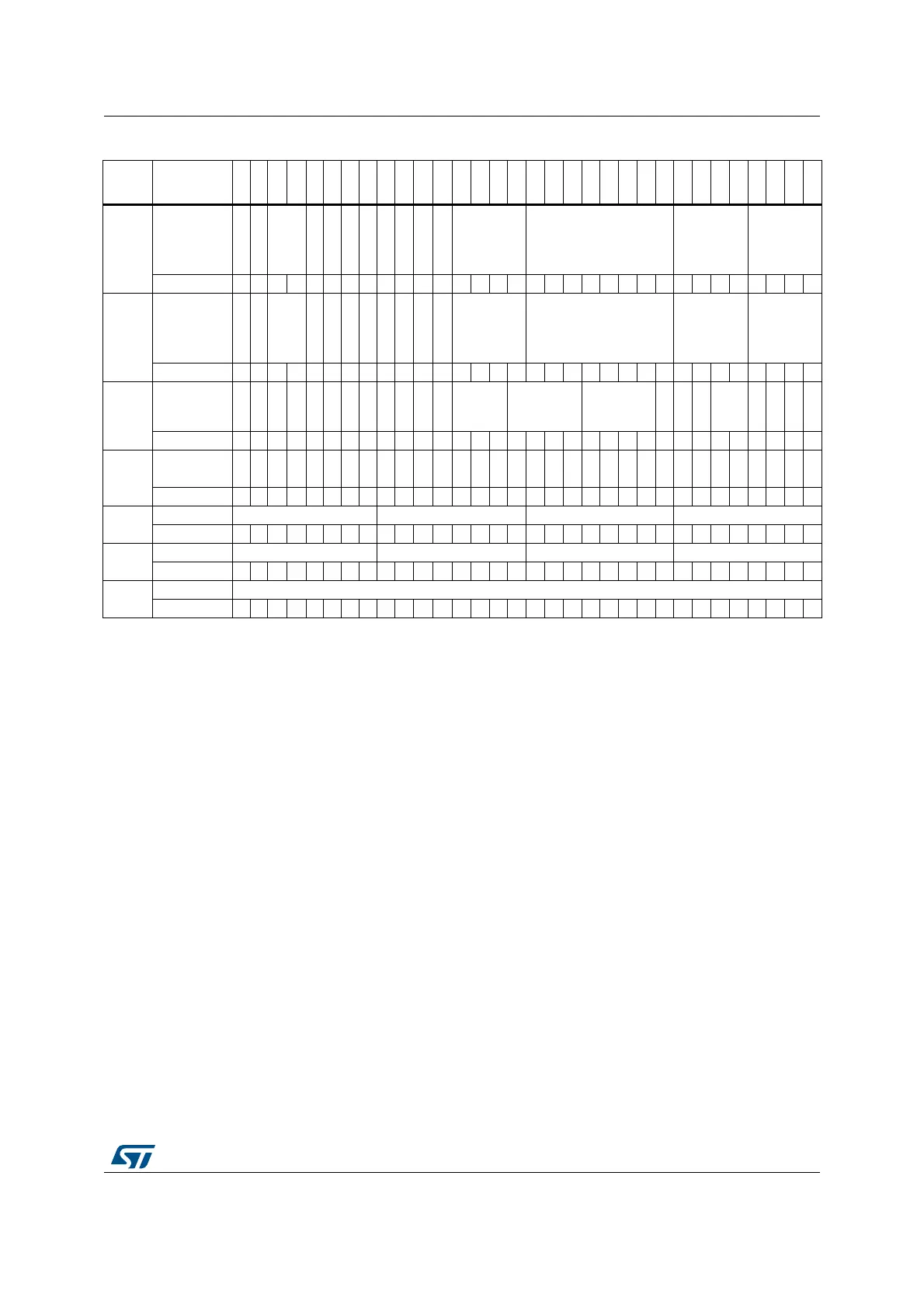

Table 97. FMC register map (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...