DocID024597 Rev 5 507/1830

RM0351 Analog-to-digital converters (ADC)

614

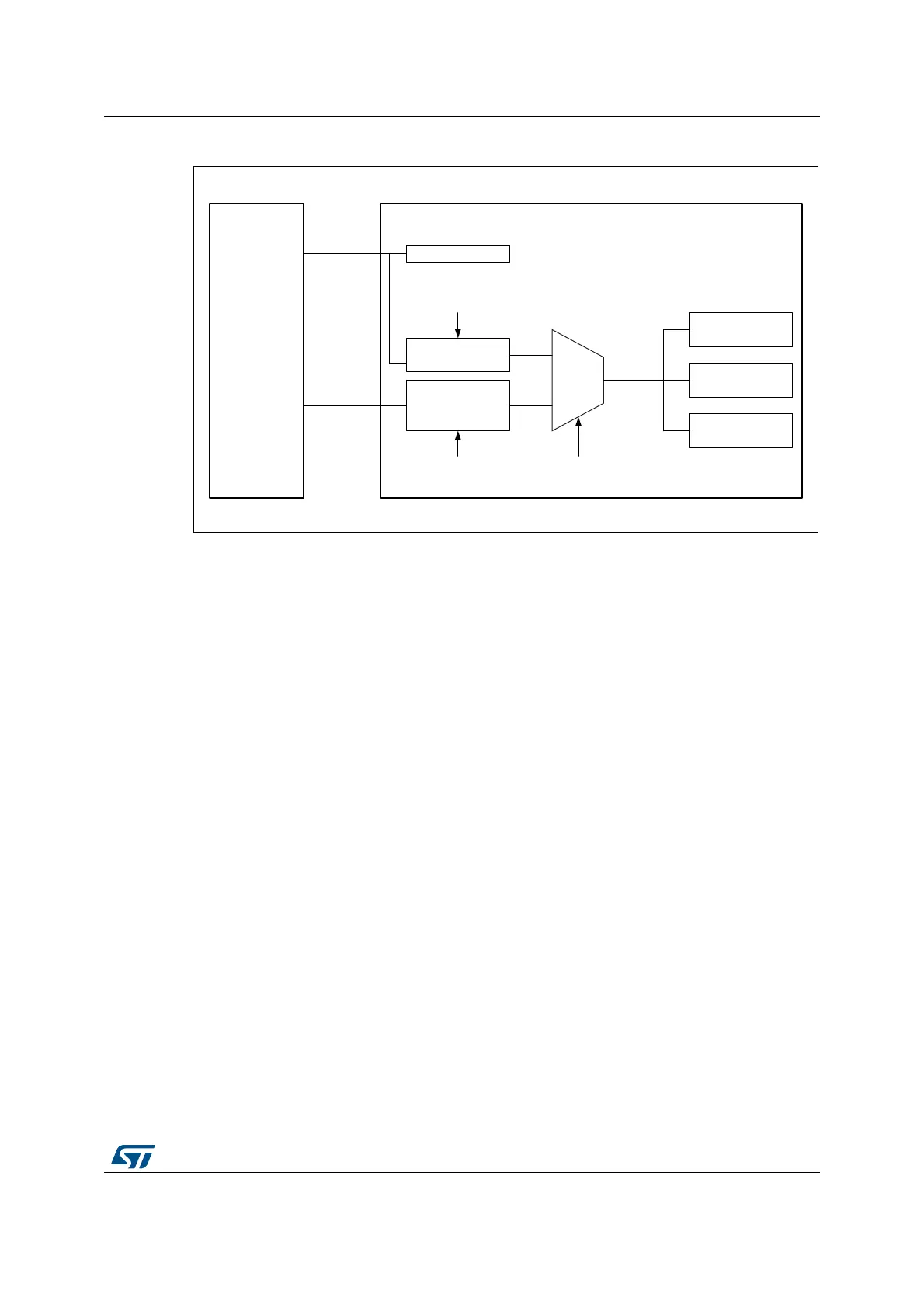

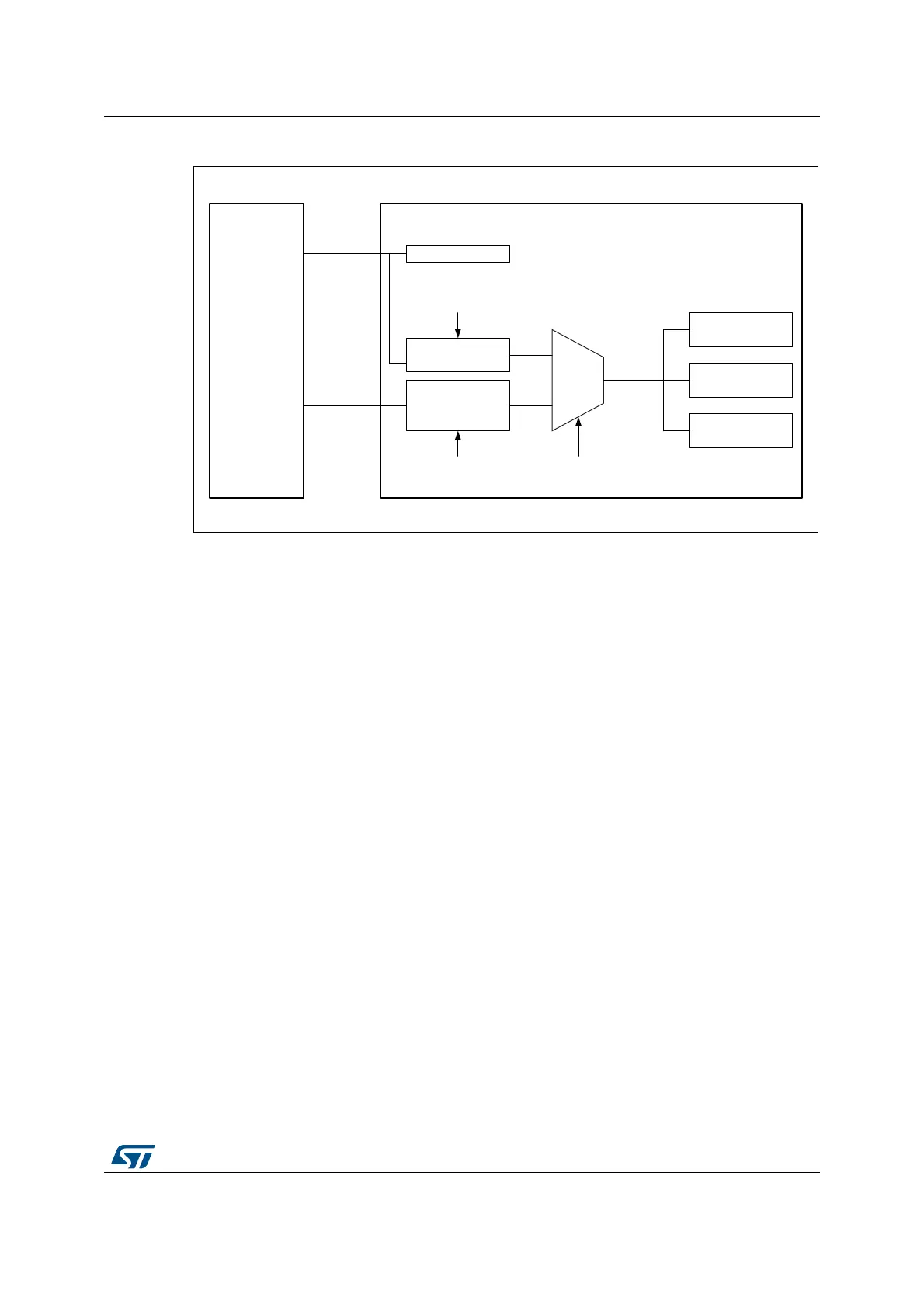

Clock ratio constraint between ADC clock and AHB clock

There are generally no constraints to be respected for the ratio between the ADC clock and

the AHB clock except if some injected channels are programmed. In this case, it is

mandatory to respect the following ratio:

• F

HCLK

>= F

ADC

/ 4 if the resolution of all channels are 12-bit or 10-bit

• F

HCLK

>= F

ADC

/ 3 if there are some channels with resolutions equal to 8-bit (and none

with lower resolutions)

• F

HCLK

>= F

ADC

/ 2 if there are some channels with resolutions equal to 6-bit

Figure 67. ADC clock scheme

069

2WKHUV

5&&

5HVHWDQG

FORFN

FRQWUROOHU

$'&$'&DQG$'&

$+%LQWHUIDFH

$QDORJ$'&

PDVWHU

$QDORJ$'&

VODYH

$QDORJ$'&

VLQJOH

RURU

%LWV35(&>@

RI$'&[B&&5

%LWV&.02'(>@

RI$'&[B&&5

+&/.

$'&B&.

%LWV&.02'(>@

RI$'&[B&&5

Loading...

Loading...