Analog-to-digital converters (ADC) RM0351

602/1830 DocID024597 Rev 5

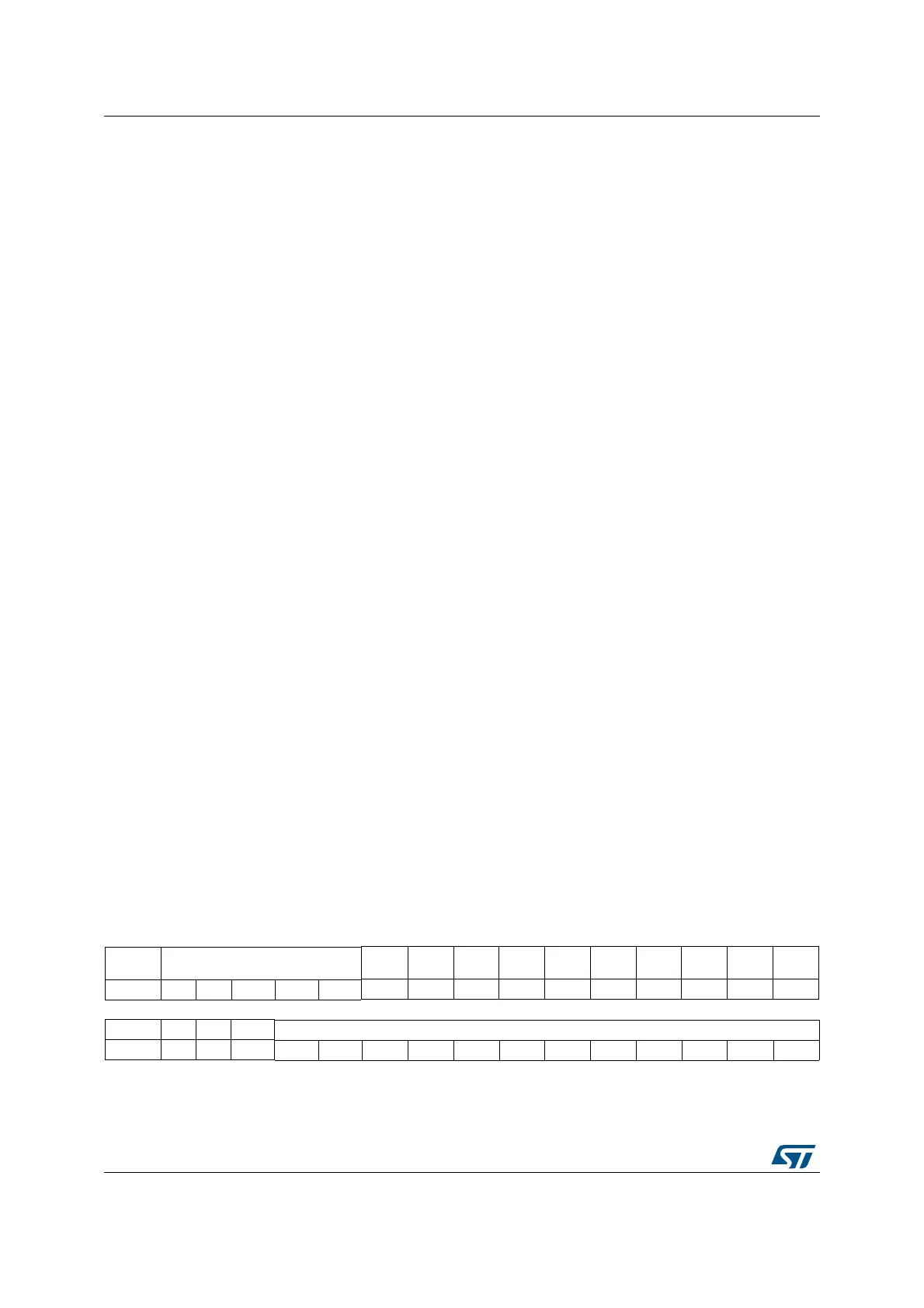

18.6.17 ADC offset register (ADC_OFRy) (y=1..4)

Address offset: 0x60, 0x64, 0x68, 0x6C

Reset value: 0x0000 0000

Bits 7:6 JEXTEN[1:0]: External Trigger Enable and Polarity Selection for injected channels

These bits are set and cleared by software to select the external trigger polarity and enable

the trigger of an injected group.

00: If JQDIS=0 (queue enabled), Hardware and software trigger detection disabled

00: If JQDIS=1 (queue disabled), Hardware trigger detection disabled (conversions can be

launched by software)

01: Hardware trigger detection on the rising edge

10: Hardware trigger detection on the falling edge

11: Hardware trigger detection on both the rising and falling edges

Note: Software is allowed to write these bits at any time, once the ADC is enabled (ADEN=1).

If JQM=1 and if the Queue of Context becomes empty, the software and hardware

triggers of the injected sequence are both internally disabled (refer to Section 18.4.21:

Queue of context for injected conversions)

Bits 5:2 JEXTSEL[3:0]: External Trigger Selection for injected group

These bits select the external event used to trigger the start of conversion of an injected

group:

0000: Event 0

0001: Event 1

0010: Event 2

0011: Event 3

0100: Event 4

0101: Event 5

0110: Event 6

0111: Event 7

...

1111: Event 15

Note: Software is allowed to write these bits at any time, once the ADC is enabled (ADEN=1).

Bits 1:0 JL[1:0]: Injected channel sequence length

These bits are written by software to define the total number of conversions in the injected

channel conversion sequence.

00: 1 conversion

01: 2 conversions

10: 3 conversions

11: 4 conversions

Note: Software is allowed to write these bits at any time, once the ADC is enabled (ADEN=1).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OFFSETy

_EN

OFFSETy_CH[4:0] Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. OFFSETy[11:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...