Digital camera interface (DCMI) RM0351

664/1830 DocID024597 Rev 5

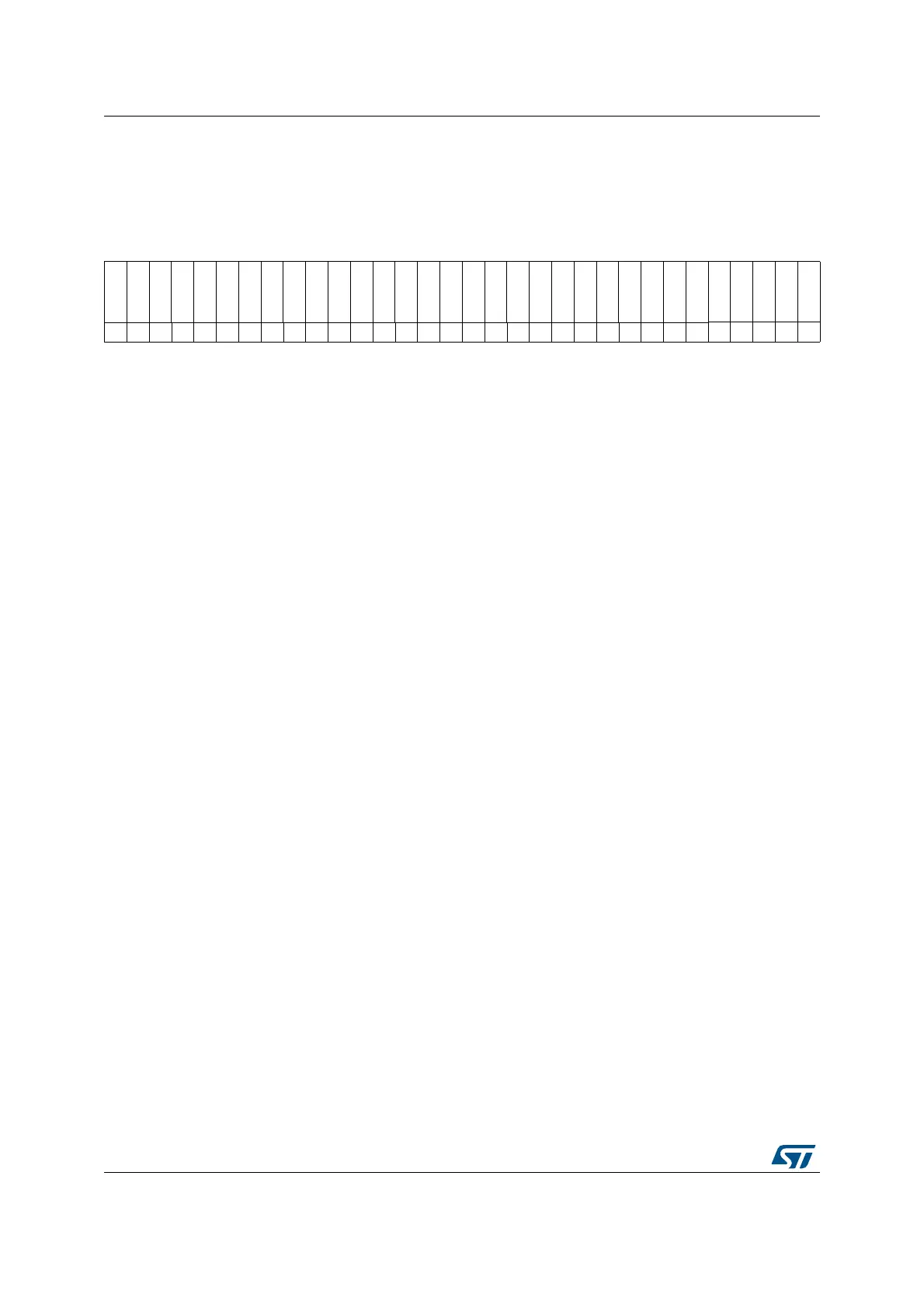

20.7.4 DCMI interrupt enable register (DCMI_IER)

Address offset: 0x0C

Reset value: 0x0000 0x0000

The DCMI_IER register is used to enable interrupts. When one of the DCMI_IER bits is set,

the corresponding interrupt is enabled. This register is accessible in both read and write.

313029282726252423222120191817161514131211109876543210

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

LINE_IE

VSYNC_IE

ERR_IE

OVR_IE

FRAME_IE

rw rw rw rw rw

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 LINE_IE: Line interrupt enable

0: No interrupt generation when the line is received

1: An Interrupt is generated when a line has been completely received

Bit 3 VSYNC_IE: DCMI_VSYNC interrupt enable

0: No interrupt generation

1: An interrupt is generated on each DCMI_VSYNC transition from the inactive to

the active state

The active state of the DCMI_VSYNC signal is defined by the VSPOL bit.

Bit 2 ERR_IE: Synchronization error interrupt enable

0: No interrupt generation

1: An interrupt is generated if the embedded synchronization codes are not

received in the correct order.

Note: This bit is available only in embedded synchronization mode.

Bit 1 OVR_IE: Overrun interrupt enable

0: No interrupt generation

1: An interrupt is generated if the DMA was not able to transfer the last data

before new data (32-bit) are received.

Bit 0 FRAME_IE: Capture complete interrupt enable

0: No interrupt generation

1: An interrupt is generated at the end of each received frame/crop window (in

crop mode).

Loading...

Loading...