DocID024597 Rev 5 697/1830

RM0351 Operational amplifiers (OPAMP)

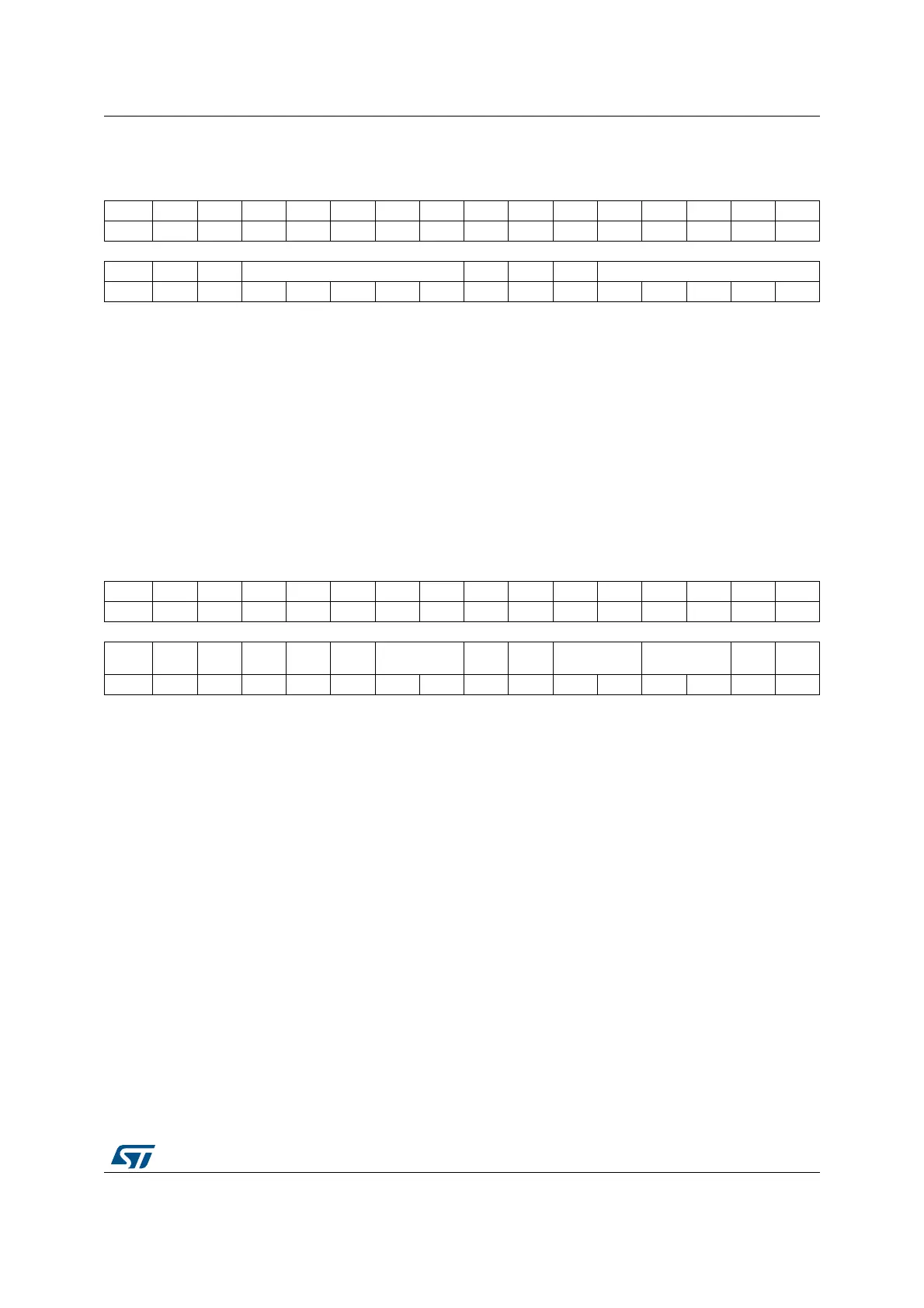

699

Reset value: 0x0000 XXXX (factory trimmed values)

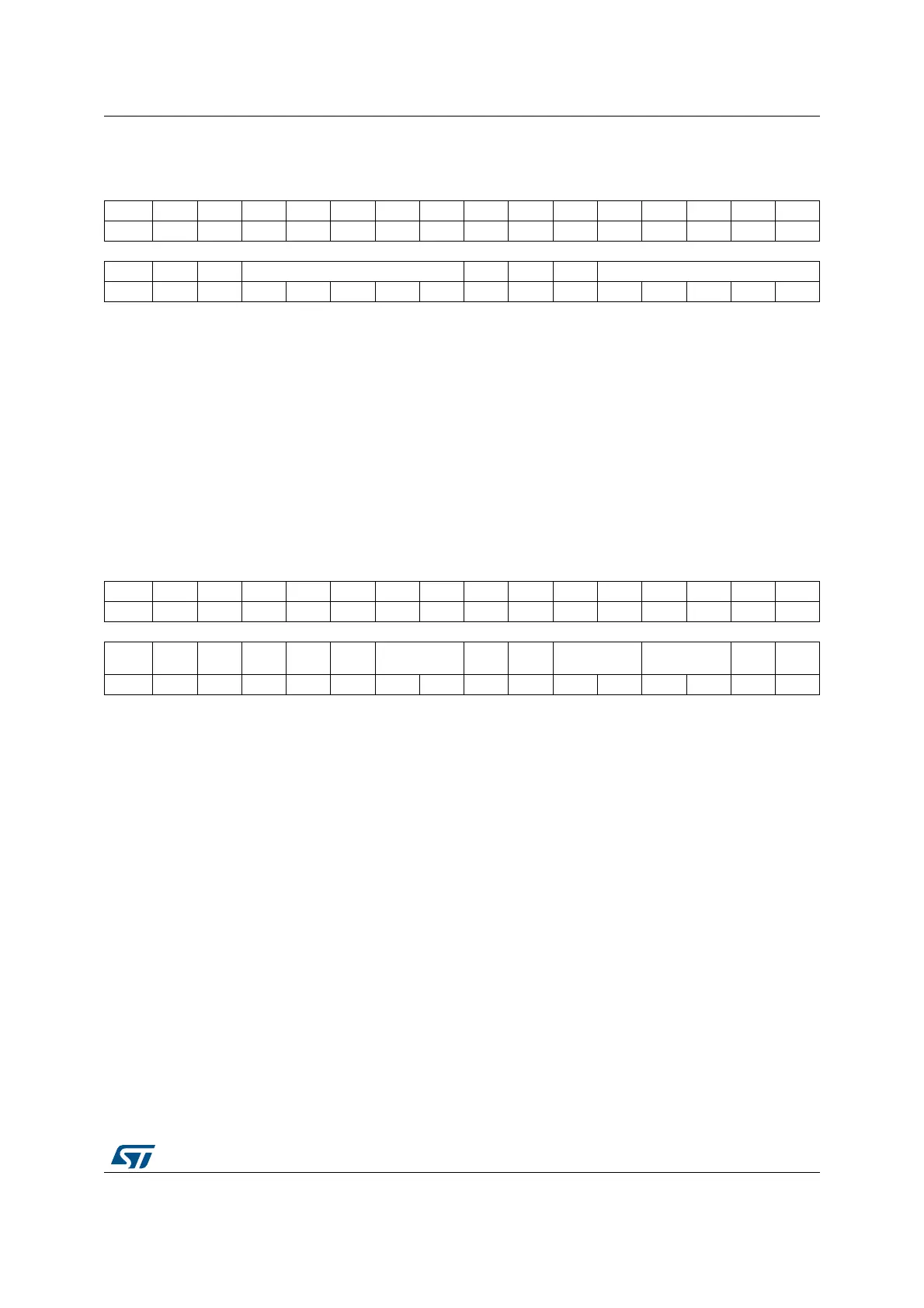

23.5.4 OPAMP2 control/status register (OPAMP2_CSR)

Address offset: 0x10

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. TRIMLPOFFSETP Res. Res. Res. TRIMLPOFFSETN

rw rw rw rw rw rw rw rw rw rw

Bits 31:13 Reserved, must be kept at reset value.

Bits 12:8 TRIMLPOFFSETP[4:0]: Low-power mode trim for PMOS differential pairs

Bits 7:5 Reserved, must be kept at reset value.

Bits 4:0 TRIMLPOFFSETN[4:0]: Low-power mode trim for NMOS differential pairs

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

CAL

OUT

USER

TRIM

CAL

SEL

CALON Res.

VP_

SEL

VM_SEL Res. Res. PGA_GAIN OPAMODE

OPA

LPM

OPAEN

r rwrwrw rwrwrw rwrwrw w rwrw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 CALOUT: Operational amplifier calibration output

During calibration mode offset is trimmed when this signal toggle.

Bit 14 USERTRIM: allows to switch from ‘factory’ AOP offset trimmed values to AOP offset ‘user’

trimmed values

This bit is active for both mode normal and low-power.

0: ‘factory’ trim code used

1: ‘user’ trim code used

Bit 13 CALSEL: Calibration selection

0: NMOS calibration (200mV applied on OPAMP inputs)

1: PMOS calibration (VDDA-200mV applied on OPAMP inputs)

Bit 12 CALON: Calibration mode enabled

0: Normal mode

1: Calibration mode (all switches opened by HW)

Bit 11 Reserved, must be kept at reset value.

Bit 10 VP_SEL: Non inverted input selection

0: GPIO connected to VINP

1: DAC connected to VINP

Loading...

Loading...