True Random Number Generator (RNG) RM0351

814/1830 DocID024597 Rev 5

27.8 RNG registers

The RNG is associated with a control register, a data register and a status register.

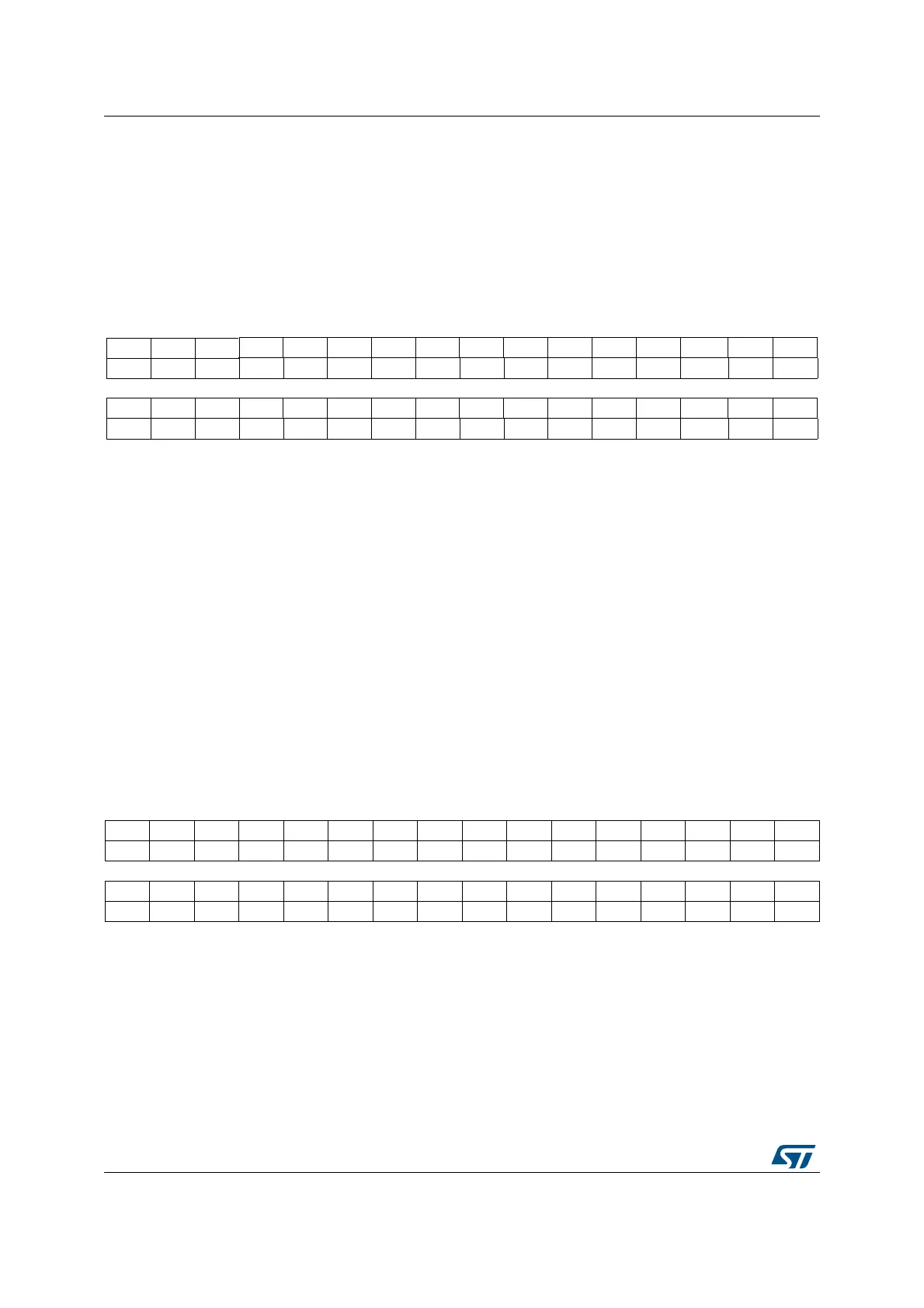

27.8.1 RNG control register (RNG_CR)

Address offset: 0x000

Reset value: 0x0000 0000

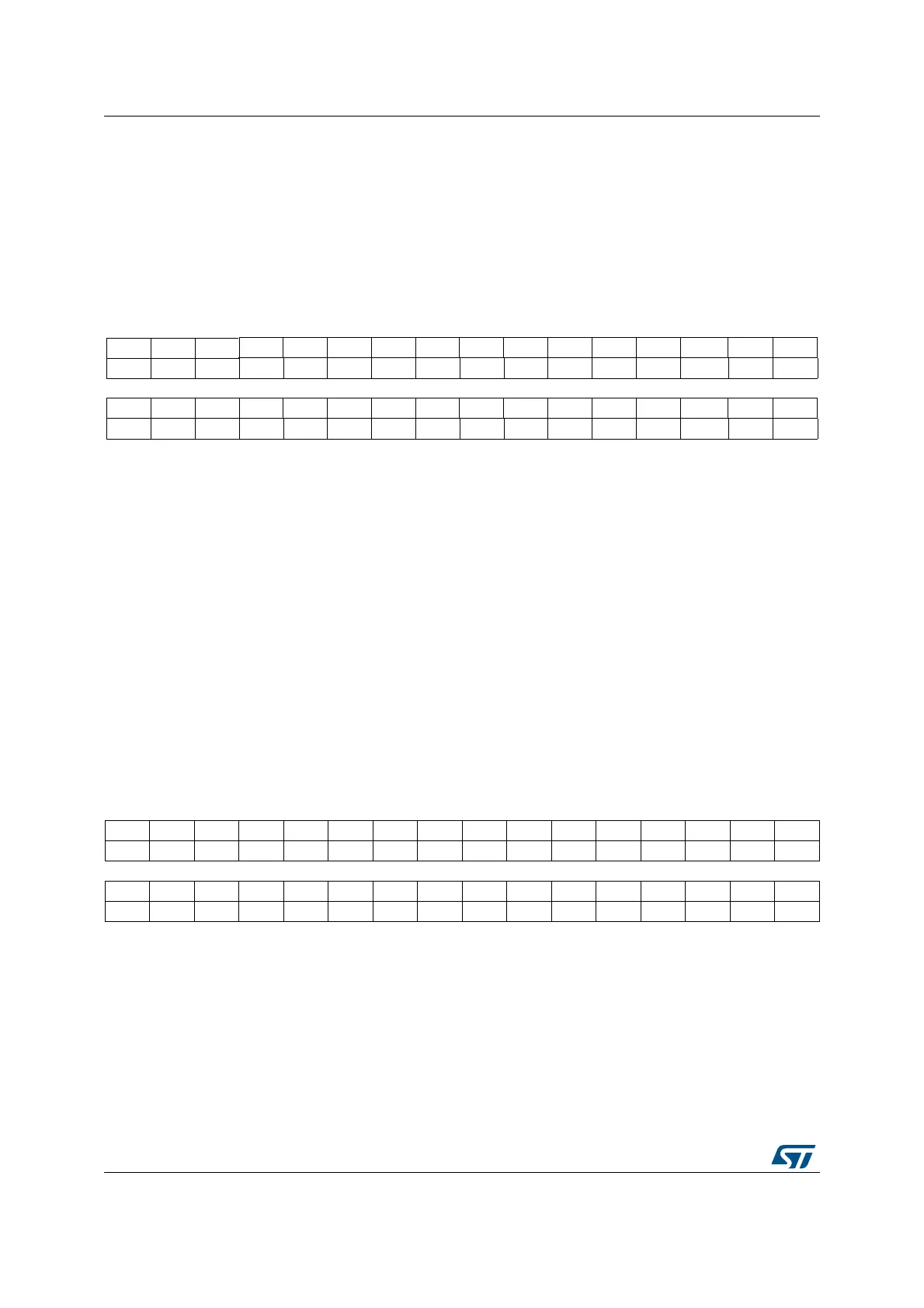

27.8.2 RNG status register (RNG_SR)

Address offset: 0x004

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. IE RNGEN Res. Res.

rw rw

Bits 31:4 Reserved, must be kept at reset value

Bit 3 IE: Interrupt Enable

0: RNG Interrupt is disabled

1: RNG Interrupt is enabled. An interrupt is pending as soon as DRDY=’1’, SEIS=’1’ or

CEIS=’1’ in the RNG_SR register.

Bit 2 RNGEN: True random number generator enable

0: True random number generator is disabled. Analog noise sources are powered off and

logic clocked by the RNG clock is gated.

1: True random number generator is enabled.

Bits 1:0 Reserved, must be kept at reset value

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. SEIS CEIS Res. Res. SECS CECS DRDY

rc_w0 rc_w0 r r r

Loading...

Loading...