DocID024597 Rev 5 967/1830

RM0351 Advanced-control timers (TIM1/TIM8)

981

Output compare mode

30.4.24 TIM1/TIM8 capture/compare register 5 (TIMx_CCR5)

Address offset: 0x58

Reset value: 0x0000 0000

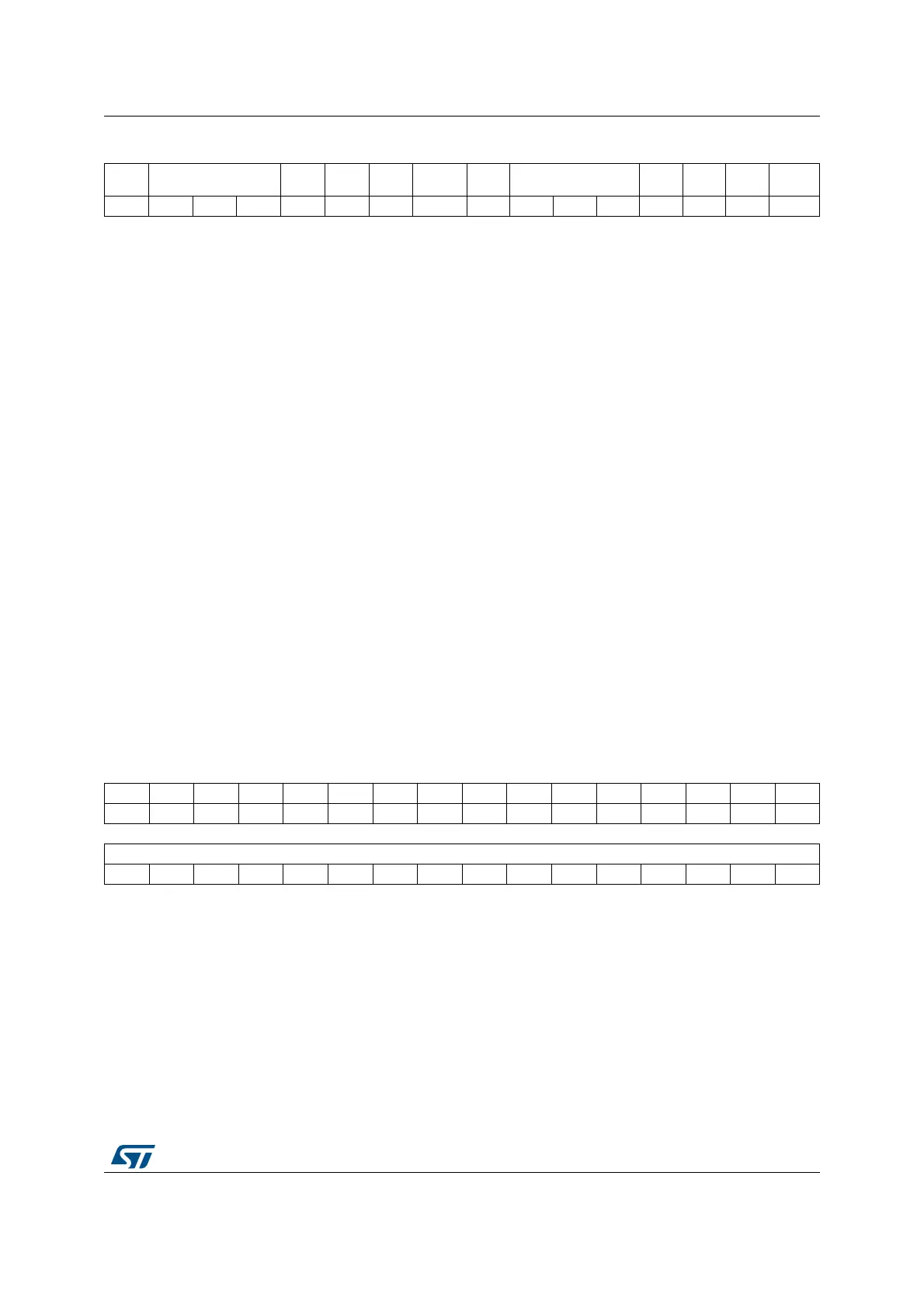

1514131211109 8 7654321 0

OC6

CE

OC6M[2:0]

OC6

PE

OC6FE Res. Res.

OC5

CE.

OC5M[2:0] OC5PE OC5FE Res. Res.

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:25 Reserved, must be kept at reset value.

Bit 24 OC6M[3]: Output Compare 6 mode - bit 3

Bits 23:17 Reserved, must be kept at reset value.

Bit 16 OC5M[3]: Output Compare 5 mode - bit 3

Bit 15 OC6CE: Output compare 6 clear enable

Bits 14:12 OC6M: Output compare 6 mode

Bit 11 OC6PE: Output compare 6 preload enable

Bit 10 OC6FE: Output compare 6 fast enable

Bits 9:8 Reserved, must be kept at reset value.

Bit 7 OC5CE: Output compare 5 clear enable

Bits 6:4 OC5M: Output compare 5 mode

Bit 3 OC5PE: Output compare 5 preload enable

Bit 2 OC5FE: Output compare 5 fast enable

Bits 1:0 Reserved, must be kept at reset value.

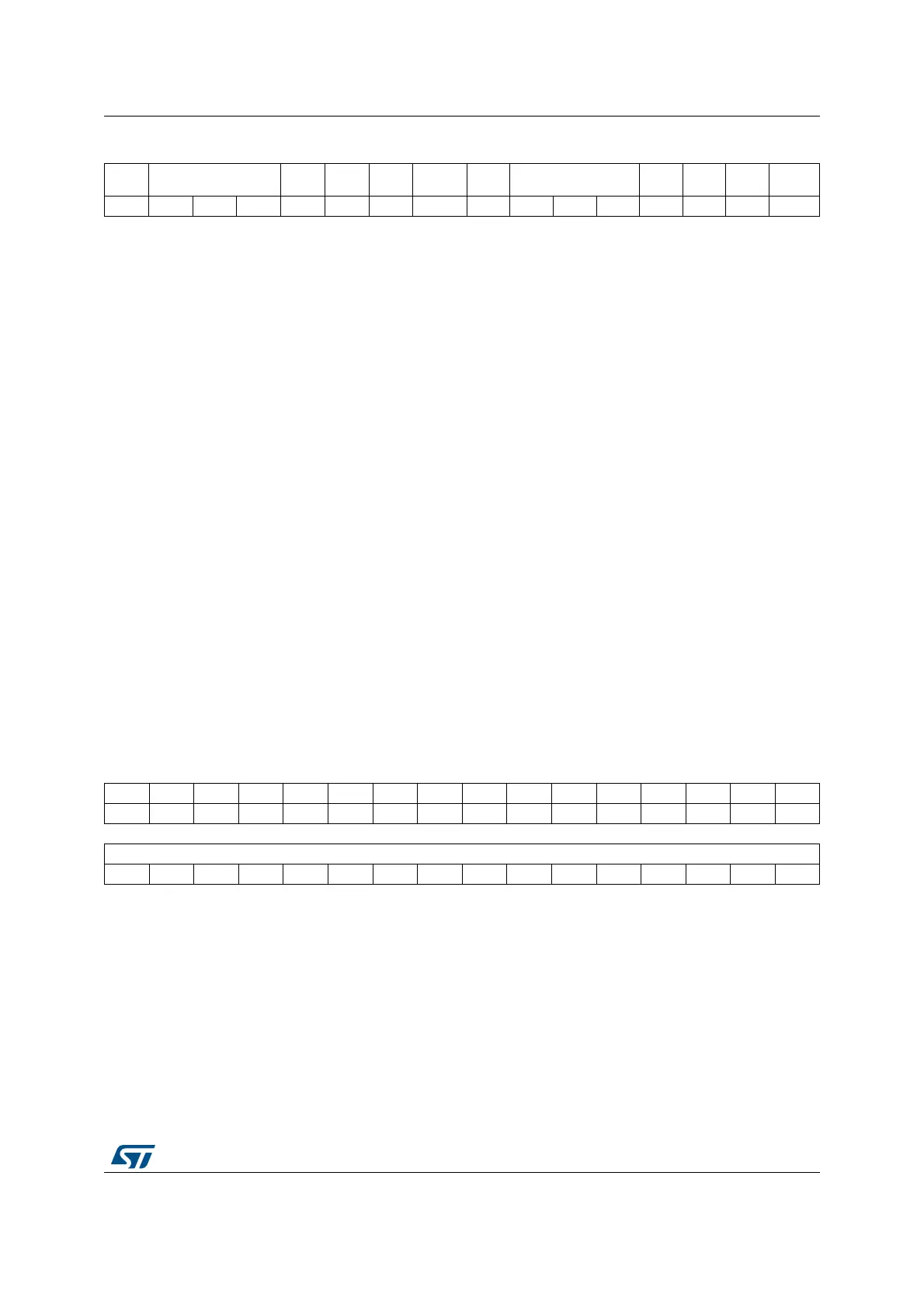

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

GC5C3 GC5C2 GC5C1 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw rw

1514131211109876543210

CCR5[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...