Advanced-control timers (TIM1/TIM8) RM0351

970/1830 DocID024597 Rev 5

Note: Refer to Figure 233: TIM1 ETR input circuitry and to Figure 255: Break and Break2 circuitry

overview.

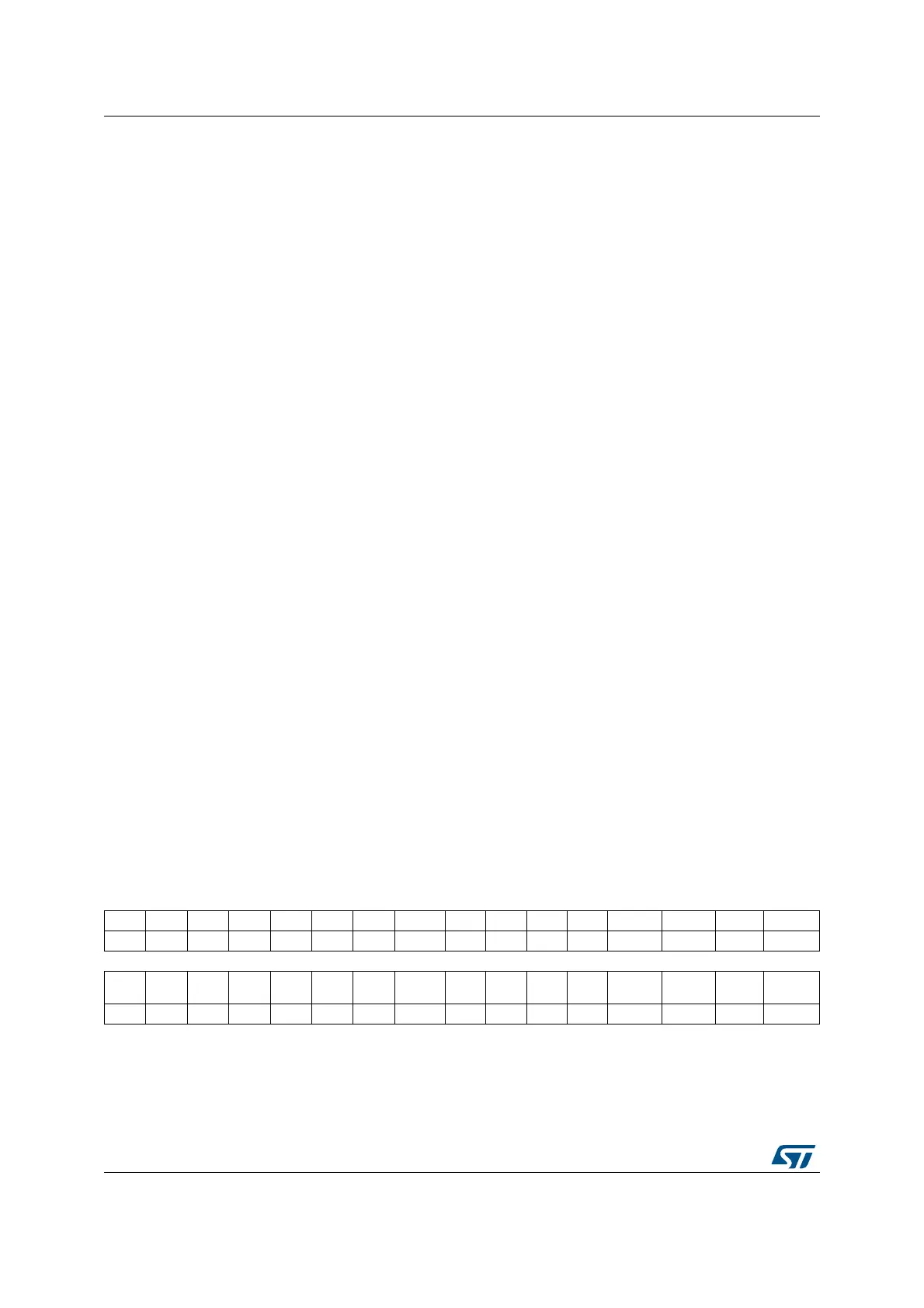

30.4.27 TIM1 option register 3 (TIM1_OR3)

Address offset: 0x64

Reset value: 0x0000 0001

Bit 8 BKDF1BK0E: BRK dfsdm1_break[0] enable

This bit enables the dfsdm1_break[0] for the timer’s BRK input. dfsdm1_break[0] output is

‘ORed’ with the other BRK sources.

0: dfsdm1_break[0] input disabled

1: dfsdm1_break[0] input enabled

Note: This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

Bits 7:3 Reserved, must be kept at reset value

Bit 2 BKCMP2E: BRK COMP2 enable

This bit enables the COMP2 for the timer’s BRK input. COMP2 output is ‘ORed’ with the

other BRK sources.

0: COMP2 input disabled

1: COMP2 input enabled

Note: This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

Bit 1 BKCMP1E: BRK COMP1 enable

This bit enables the COMP1 for the timer’s BRK input. COMP1 output is ‘ORed’ with the

other BRK sources.

0: COMP1 input disabled

1: COMP1 input enabled

Note: This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

Bit 0 BKINE: BRK BKIN input enable

This bit enables the BKIN alternate function input for the timer’s BRK input. BKIN input is

‘ORed’ with the other BRK sources.

0: BKIN input disabled

1: BKIN input enabled

Note: This bit can not be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

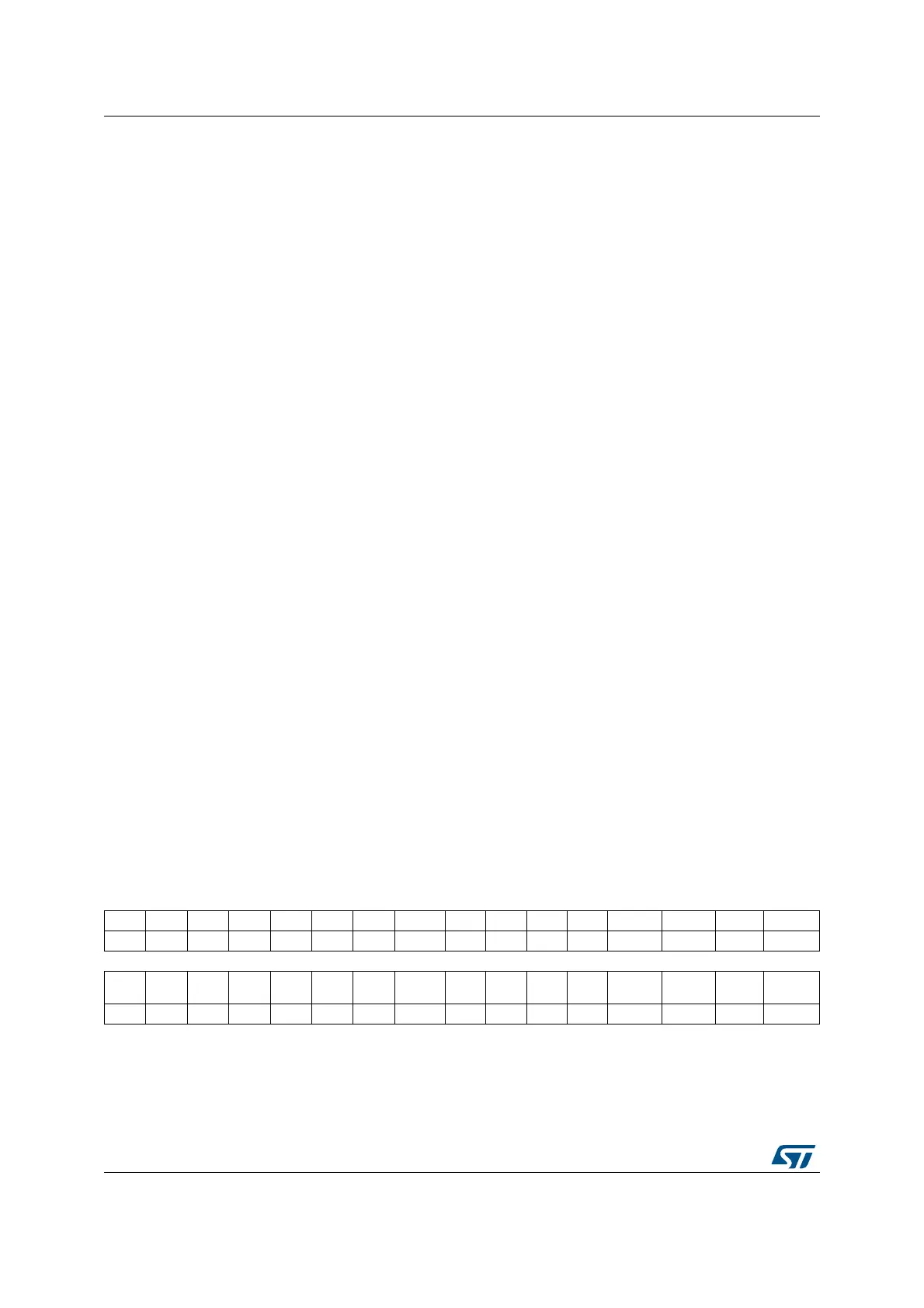

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res.

BK2C

MP2P

BK2C

MP1P

BK2IN

P

BK2DF1

BK1E

Res. Res. Res. Res. Res.

BK2CMP

2E

BK2CM

P1E

BK2INE

rw rw rw rw rw rw rw

Bits 31:12 Reserved, must be kept at reset value

Loading...

Loading...