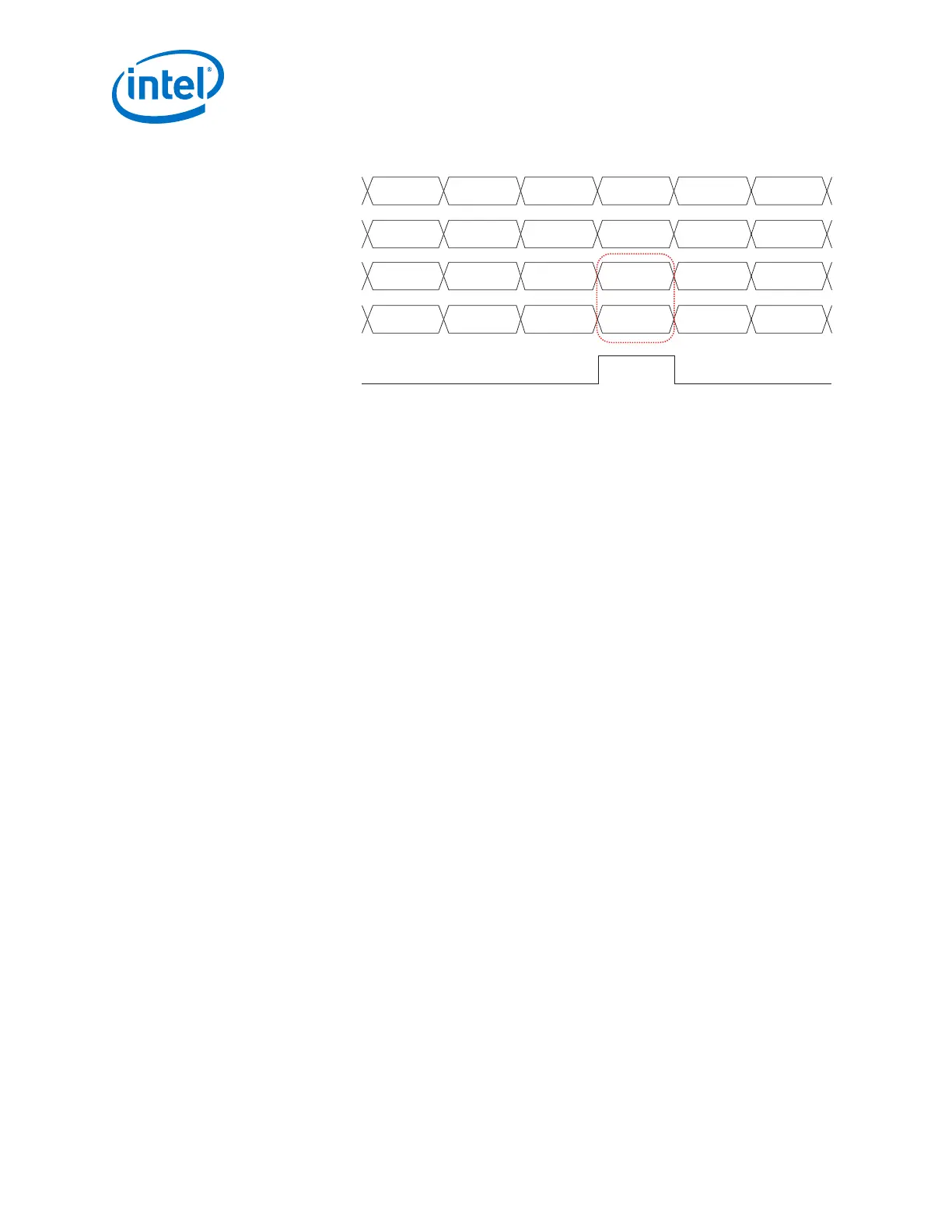

Figure 151. Rate Match FIFO Becoming Empty After Reading out the 20-Bit Word D5D6

D2 D4 D6 /K30.7/ D8 D10

D1 D3 D5 /K30.7/ D7

D9

rx_parallel_data[19:10]

rx_parallel_data[9:0]

rx_std_rmfifo_empty

D2 D4 D6 D8 D10 D12

D1 D3 D5 D7 D9

D11

tx_parallel_data[19:0]

tx_parallel_data[9:0]

2.9.2.9. 8B/10B Encoder and Decoder

To enable the 8B/10B Encoder and the 8B/10B Decoder, select the Enable TX

8B/10B Encoder and Enable RX 8B/10B Decoder options on the Standard PCS

tab in the IP Editor. Platform Designer (Standard) allows implementing the 8B/10B

decoder in RX-only mode.

The following ports are added:

•

tx_datak

•

rx_datak

•

rx_runningdisp

•

rx_disperr

•

rx_errdetect

rx_datak and tx_datak indicate whether the parallel data is a control word or a

data word. The incoming 8-bit data (tx_parallel_data) and the control identifier

(tx_datak) are converted into a 10-bit data. After a power on reset, the 8B/10B

encoder takes the 10-bit data from the RD- column. Next, the encoder chooses the

10-bit data from the RD+ column to maintain neutral disparity. The running disparity

is shown by rx_runningdisp.

2.9.2.10. 8B/10B TX Disparity Control

The Disparity Control feature controls the running disparity of the output from the

8B/10B Decoder.

To enable TX Disparity Control, select the Enable TX 8B/10B Disparity Control

option. The following ports are added:

•

tx_forcedisp—a control signal that indicates whether a disparity value has to

be forced or not

•

tx_dispval—a signal that indicates the value of the running disparity that is

being forced

When the number of data channels is more than 1, tx_forcedisp and tx_dispval

are shown as buses in which each bit corresponds to one channel.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

310

Loading...

Loading...