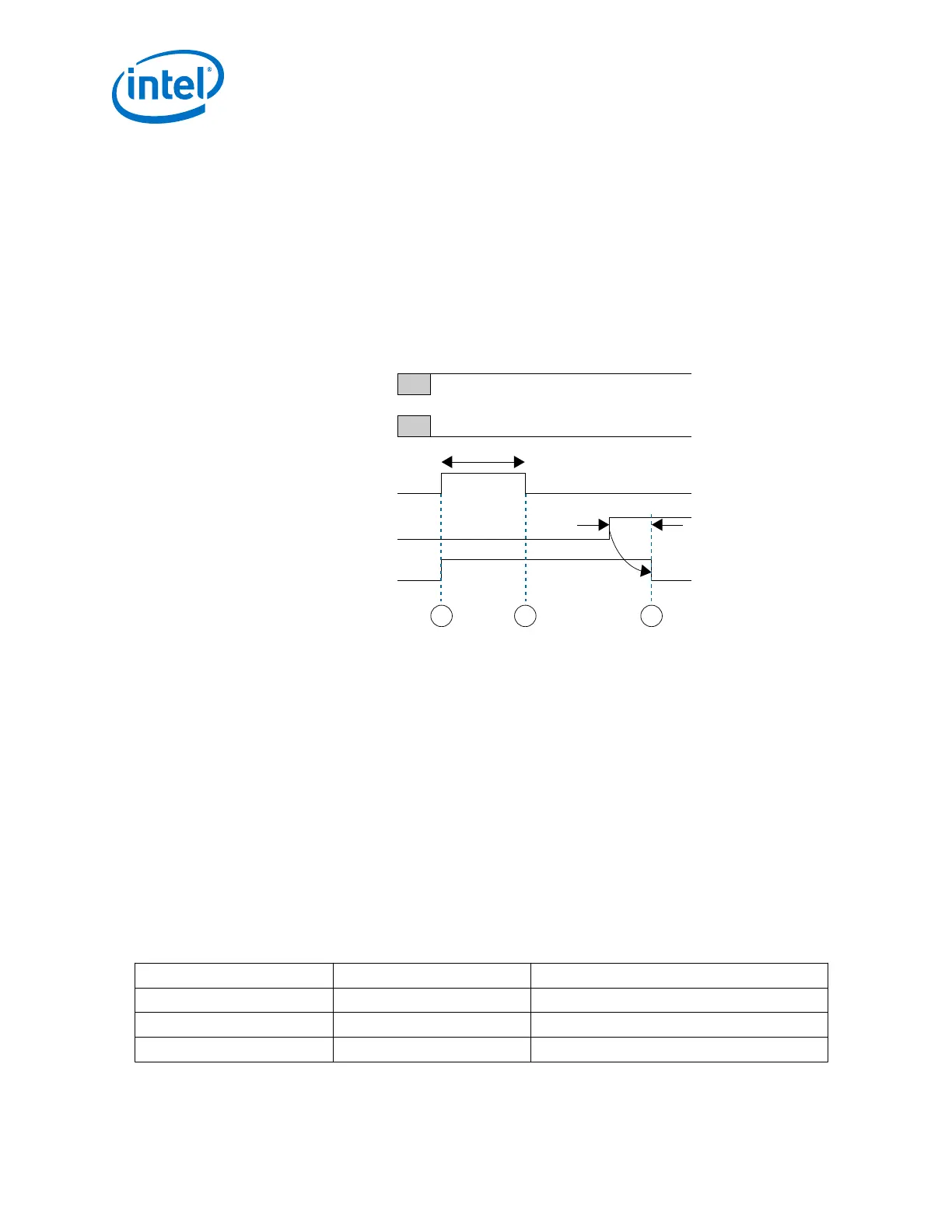

Clock Data Recovery in Auto Lock Mode

The step numbers correspond to the numbers in the following figure:

1.

Assert rx_analogreset and rx_digitalreset. Ensure that rx_cal_busy is

low. You must reset the PCS by asserting rx_digitalreset every time you

assert rx_analogreset.

2.

Deassert rx_analogreset after a minimum duration of 70 μs.

3.

Ensure rx_is_lockedtodata is asserted for t

LTD

(minimum of 4 μs) before

deasserting rx_digitalreset.

Figure 203. Resetting the Receiver During Device Operation (Auto Mode)

Device Power Up

rx_cal_busy

rx_analogreset

rx_is_lockedtodata

rx_digitalreset

1 2 3

t

req

t

LTD

min 4 μs

t

req

= 70 μs

Note:

rx_is_lockedtodata will toggle when there is no data at the receiver input.

rx_is_lockedtoref is a don't care when rx_is_lockedtodata is asserted.

Clock Data Recovery in Manual Lock Mode

Use the clock data recovery (CDR) manual lock mode to override the default CDR

automatic lock mode depending on your design requirements.

Related Information

"Transceiver PHY Reset Controller IP Core" chapter of the Altera Transceiver PHY IP

Core User Guide.

Refer to the description of the rx_digitalreset signal in the "Top-Level Signals"

table for information about using the manual lock mode.

Control Settings for CDR Manual Lock Mode

Use the following control settings to set the CDR lock mode:

Table 245. Control Settings for the CDR in Manual Lock Mode

rx_set_locktoref rx_set_locktodata CDR Lock Mode

0 0 Automatic

1 0 Manual-RX CDR LTR

X 1 Manual-RX CDR LTD

4. Resetting Transceiver Channels

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

422

Loading...

Loading...