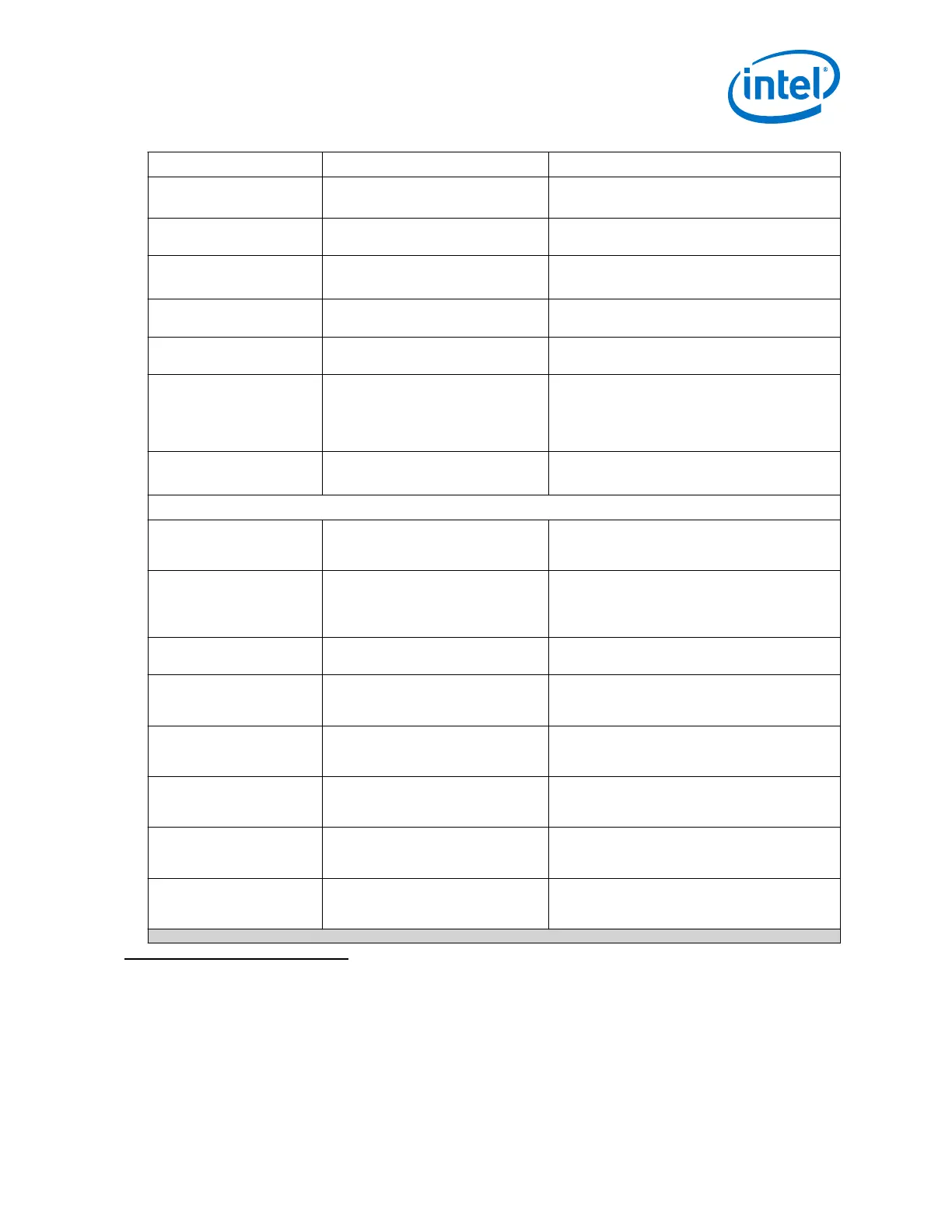

Parameter Value Description

Pre-Emphasis First Post-Tap

Polarity

Fir_post_1t_neg

Fir_post_1t_pos

Selects the polarity of the first post-tap for pre-

emphasis

Pre-Emphasis First Post-Tap

Magnitude

0-25

(31)

Selects the magnitude of the first post-tap for

pre-emphasis.

Pre-Emphasis Second Post-

Tap Polarity

Fir_post_2t_neg

Fir_post_2t_pos

Selects the polarity of the second post-tap for

pre-emphasis.

Pre-Emphasis Second Post-

Tap Magnitude

0-12

(32)

Selects the magnitude of the second post-tap for

pre-emphasis

Slew Rate Control

slew_r0 to slew_r5

Selects the slew rate of the TX output signal. Valid

values span from slowest to the fastest rate.

High-Speed Compensation Enable/Disable Enables the power-distribution network (PDN)

induced inter-symbol interference (ISI)

compensation in the TX driver. When enabled, it

reduces the PDN induced ISI jitter, but increases

the power consumption.

On-Chip termination

r_r1

r_r2

Selects the on-chip TX differential termination.

RX Analog PMA settings

Override Intel-recommended

Default settings

On/Off Enables the option to override the Intel-

recommended settings for one or more RX analog

parameters

CTLE (Continuous Time

Linear Equalizer) mode

non_s1_mode

S1_mode

Selects between the RX high gain mode

non_s1_mode or RX high data rate mode

s1_mode for the Continuous Time Linear

Equalizer (CTLE).

DC gain control of high gain

mode CTLE

No_dc_gain to stg4_gain7

Selects the DC gain of the Continuous Time Linear

Equalizer (CTLE) in high gain mode

AC Gain Control of High Gain

Mode CTLE

radp_ctle_acgain_4s_0 to

radp_ctle_acgain_4s_28

Selects the AC gain of the Continuous Time Linear

Equalizer (CTLE) in high gain mode when CTLE is

in manual mode.

AC Gain Control of High Data

Rate Mode CTLE

radp_ctle_eqz_1s_sel_0 to

Radp_ctle_eqz_1s_sel_15

Selects the AC gain of the Continuous Time Linear

Equalizer (CTLE) in high data rate mode when

CTLE is in manual mode.

Variable Gain Amplifier

(VGA) Voltage Swing Select

radp_vga_sel_0 to

radp_vga_sel_7

Selects the Variable Gain Amplifier (VGA) output

voltage swing when both the CTLE and DFE blocks

are in manual mode

Decision Feedback Equalizer

(DFE) Fixed Tap 1 Co-

efficient

radp_dfe_fxtap1_0 to

radp_dfe_fxtap1_127

Selects the co-efficient of the fixed tap 1 of the

Decision Feedback Equalizer (DFE) when

operating in manual mode

Decision Feedback Equalizer

(DFE) Fixed Tap 2 Co-

efficient

radp_dfe_fxtap2_0 to

radp_dfe_fxtap2_127

Selects the co-efficient of the fixed tap 2 of the

Decision Feedback Equalizer (DFE) when

operating in manual mode

continued...

(31)

For more information refer to Available Options table in the

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_1ST_POST_TAP section of the Analog Parameter

Settings chapter.

(32)

For more information refer to Available Options table in the

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_2ND_POST_TAP section of the Analog Parameter

Settings chapter.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

71

Loading...

Loading...