Keysight M8000 Series of BER Test Solutions User Guide 283

Setting up Generator 5

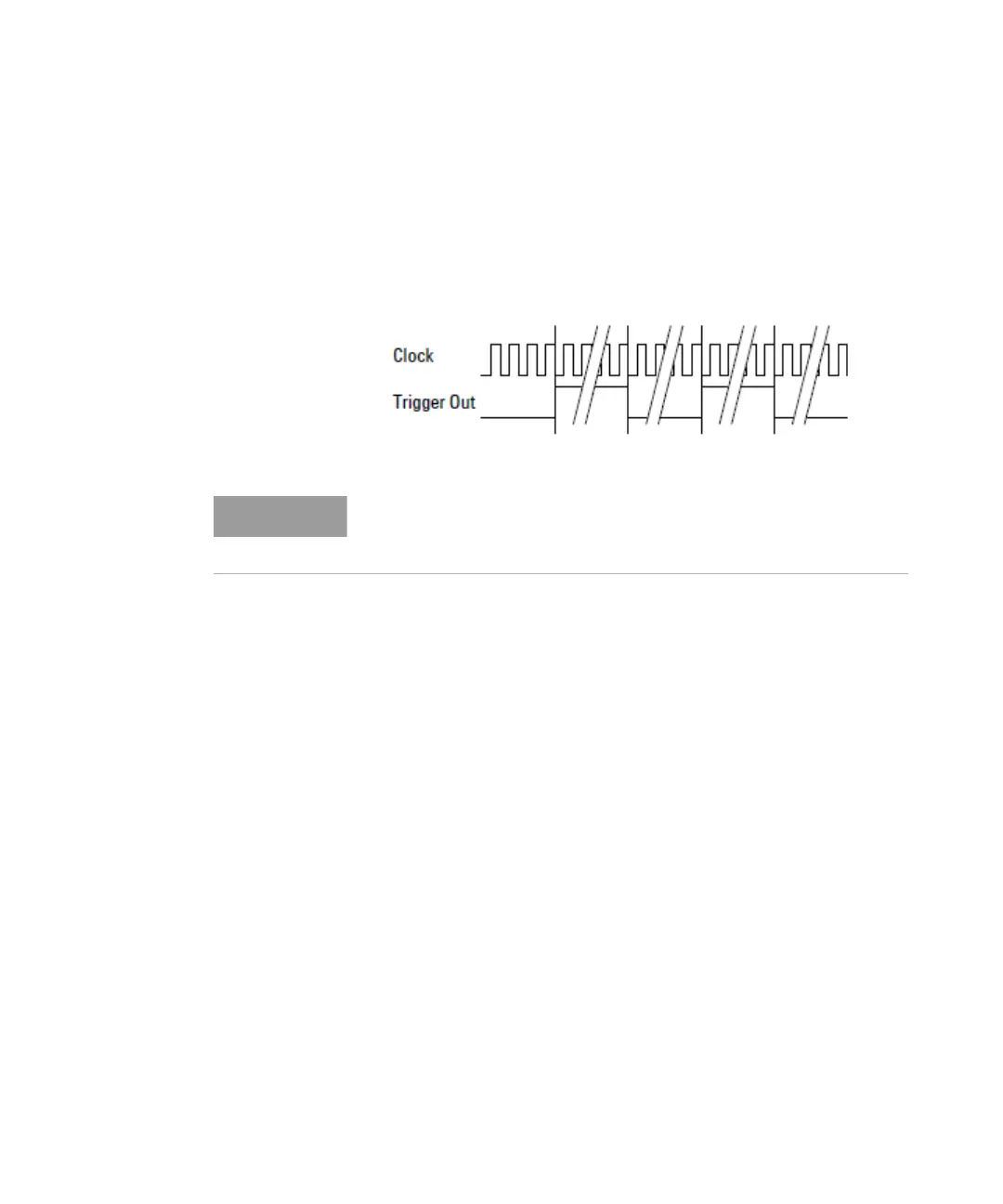

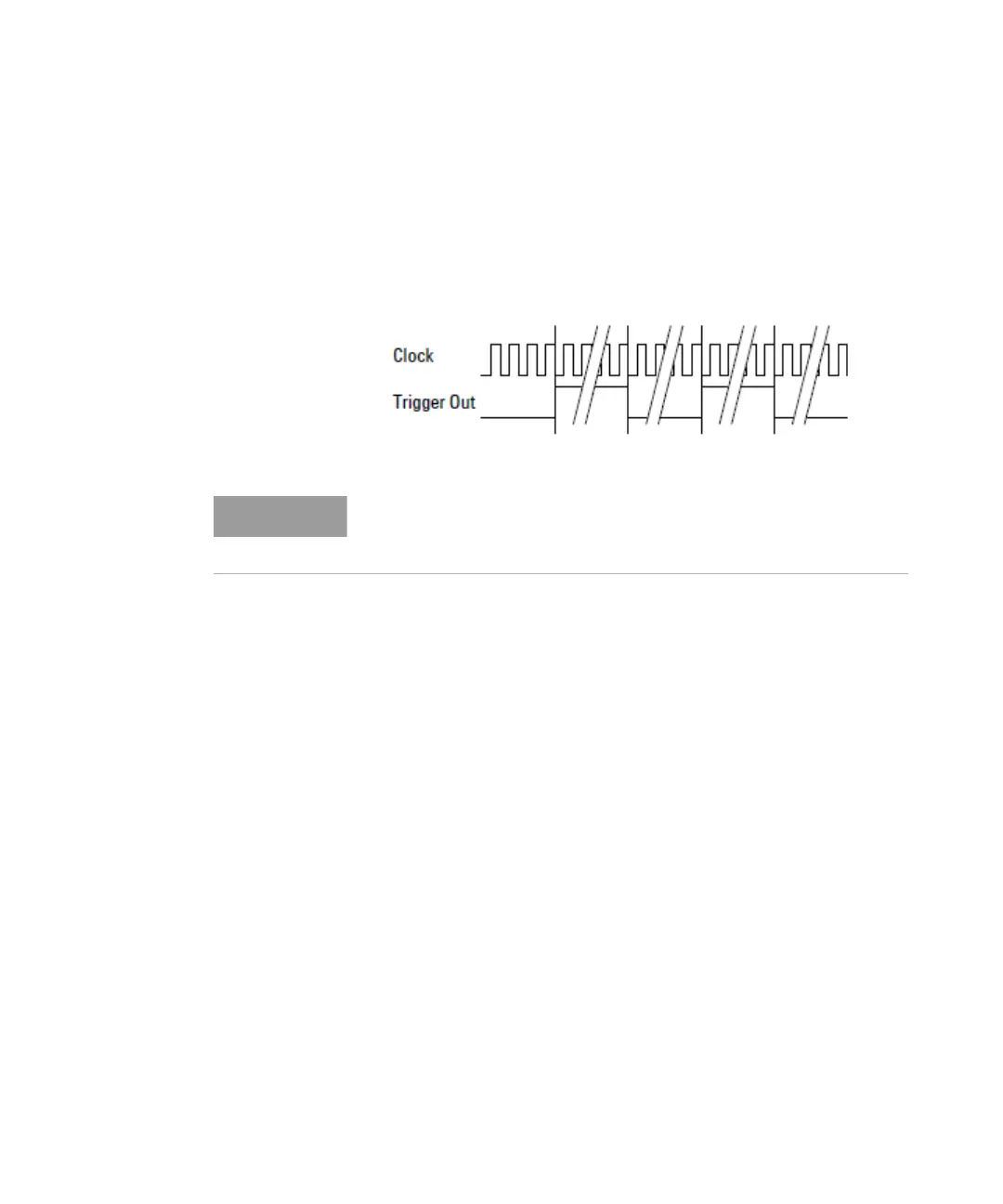

Clock Divided by n

Select this option to send a trigger signal from the Trigger/Ref Clock Out

port at every nth clock pulse. Note that the trigger signal itself consists of

n/2 bits high followed by n/2 bits low. For example, Clock divided by 8

works as shown below.

Sequence Trigger

This function becomes available after a user-defined sequence has been

downloaded to the generator.

Click this function to switch the Trigger Out port to Sequence mode.

In Sequence mode, the Trigger Out can generate a spike whenever the

execution of a block starts or restarts. Whether that happens for a

particular block or not is defined for each block individually in the

sequence expression.

If the Divider Factor n is uneven (For example 3), the clock's duty cycle

will not be 50%, but the signal will stay high for (n+1)/2 and low for

(n-1)/2. This results in a Duty Cycle Distortion (DCD) of 0.5 UI.

Loading...

Loading...