RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1174

Dec 10, 2015

(10) LIN Break Field Configuration Register/UART Configuration Register (LBFCn)

Address: F06C9H

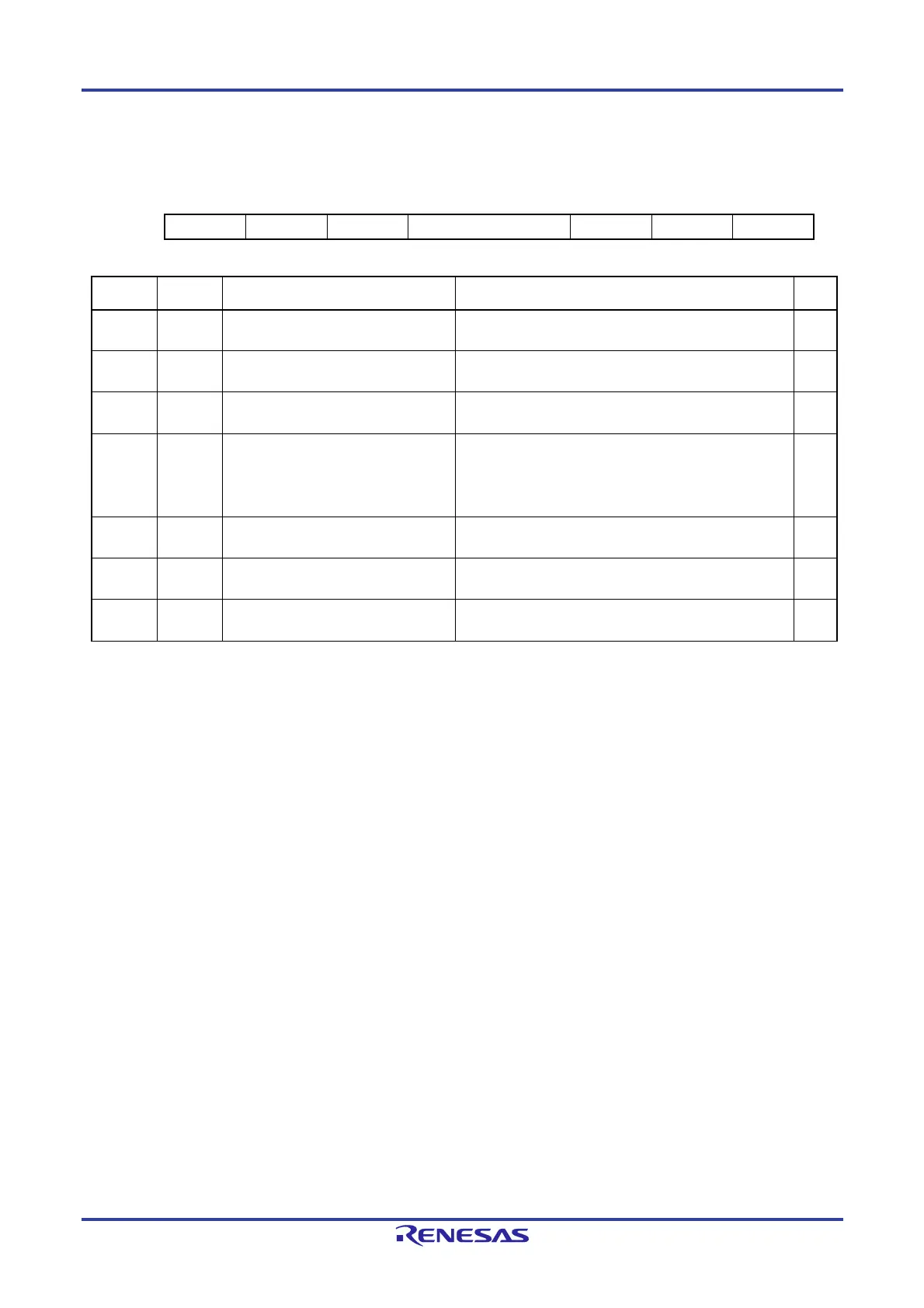

7 6 5 4 3 2 1 0

— UTPS URPS UPS[1:0] USBLS UBOS UBLS

Value after reset:

0 0 0 0 0 0 0 0

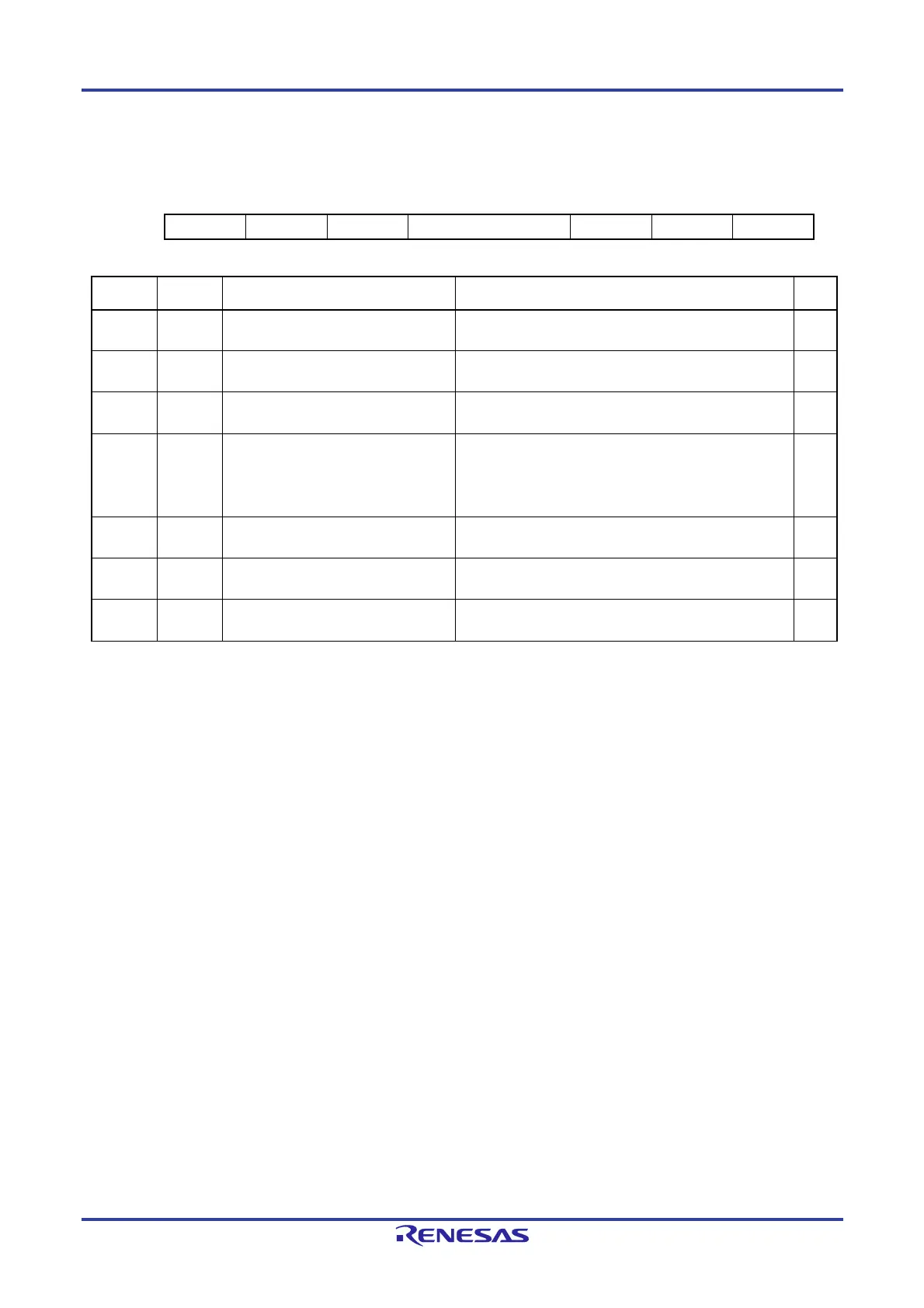

Bit Symbol Bit Name Function R/W

0 UBLS UART Character Length Select 0: 8-bit UART communication

1: 7-bit UART communication

R/W

1 UBOS UART Transfer Format Select 0: LSB first

1: MSB first

R/W

2 USBLS UART Stop Bit Length Select 0: One stop bit

1: Two stop bits

R/W

4, 3 UPS[1:0] UART Parity Select

b4 b3

0 0: No parity

0 1: Even parity

1 0: 0-parity

1 1: Odd parity

R/W

5 URPS UART Input Polarity Select 0: Reception data is input as is.

1: Reception data is reversed before being input.

R/W

6 UTPS UART Output Polarity Select 0: Transmission data is output as is.

1: Transmission data is reversed before being output.

R/W

7 — Reserved This bit is always read as 0. The write value should always

be 0.

R/W

Set the LBFCn register when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

UBLS bit (UART character length select bit)

The UBLS bit sets the length of a character of a UART communication frame.

With 0 set, a character of a frame is 8 bits long in communication.

With 1 set, a character of a frame is 7 bits long in communication.

Setting this bit is invalid when a character of a UART frame for communication is 9 bits long (the UEBE bit in the LUORn1

register is 1).

UBOS bit (UART transfer format select bit)

The UBOS bit sets the bit order of UART communication data.

With 0 set, data is transferred with the LSB first.

With 1 set, data is transferred with the MSB first.

USBLS bit (UART stop bit length select bit)

The USBLS bit sets the stop bit length in UART communication.

With 0 set, transmission is performed with 1 stop bit.

With 1 set, transmission is performed with 2 stop bits.

Loading...

Loading...