RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1183

Dec 10, 2015

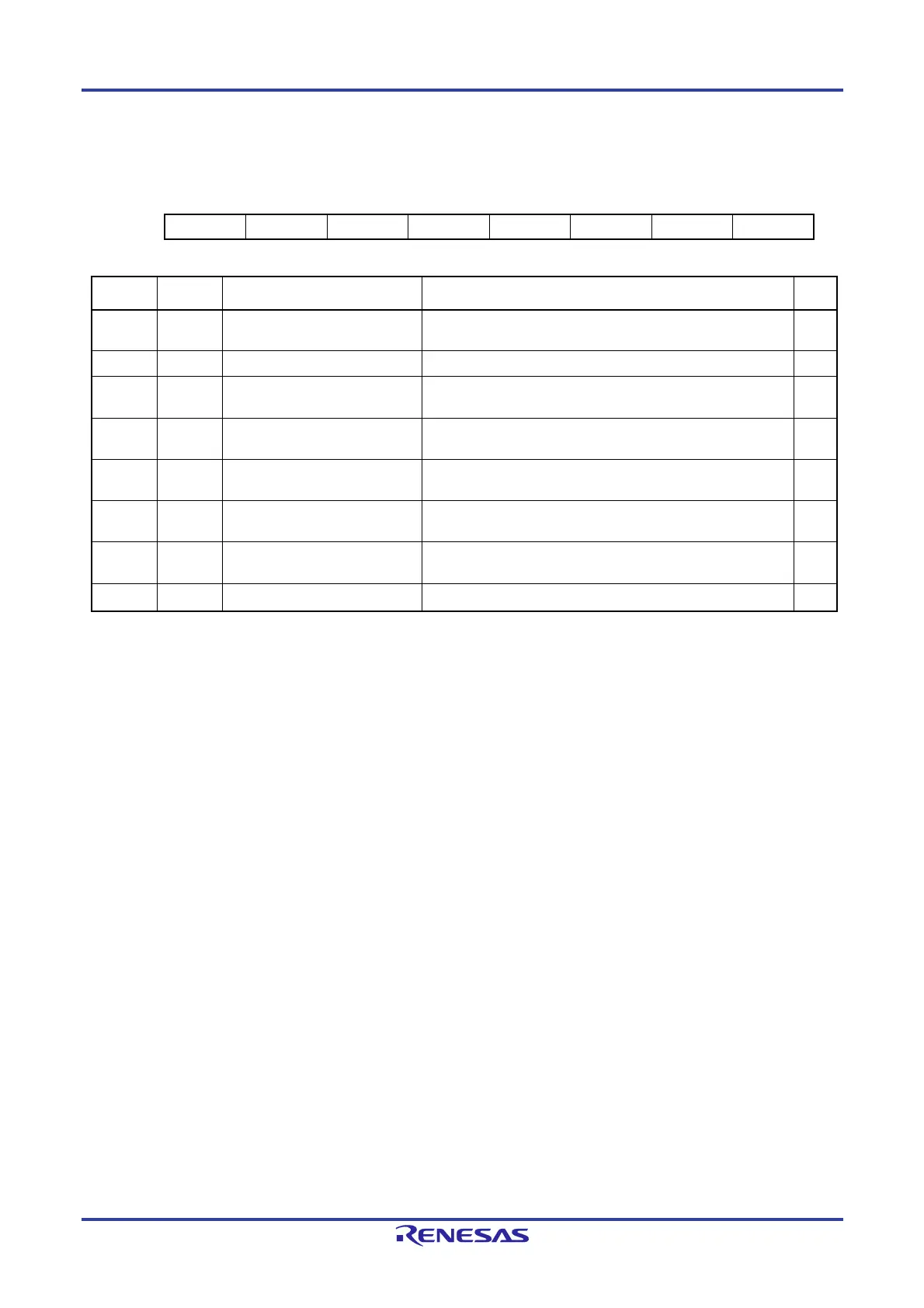

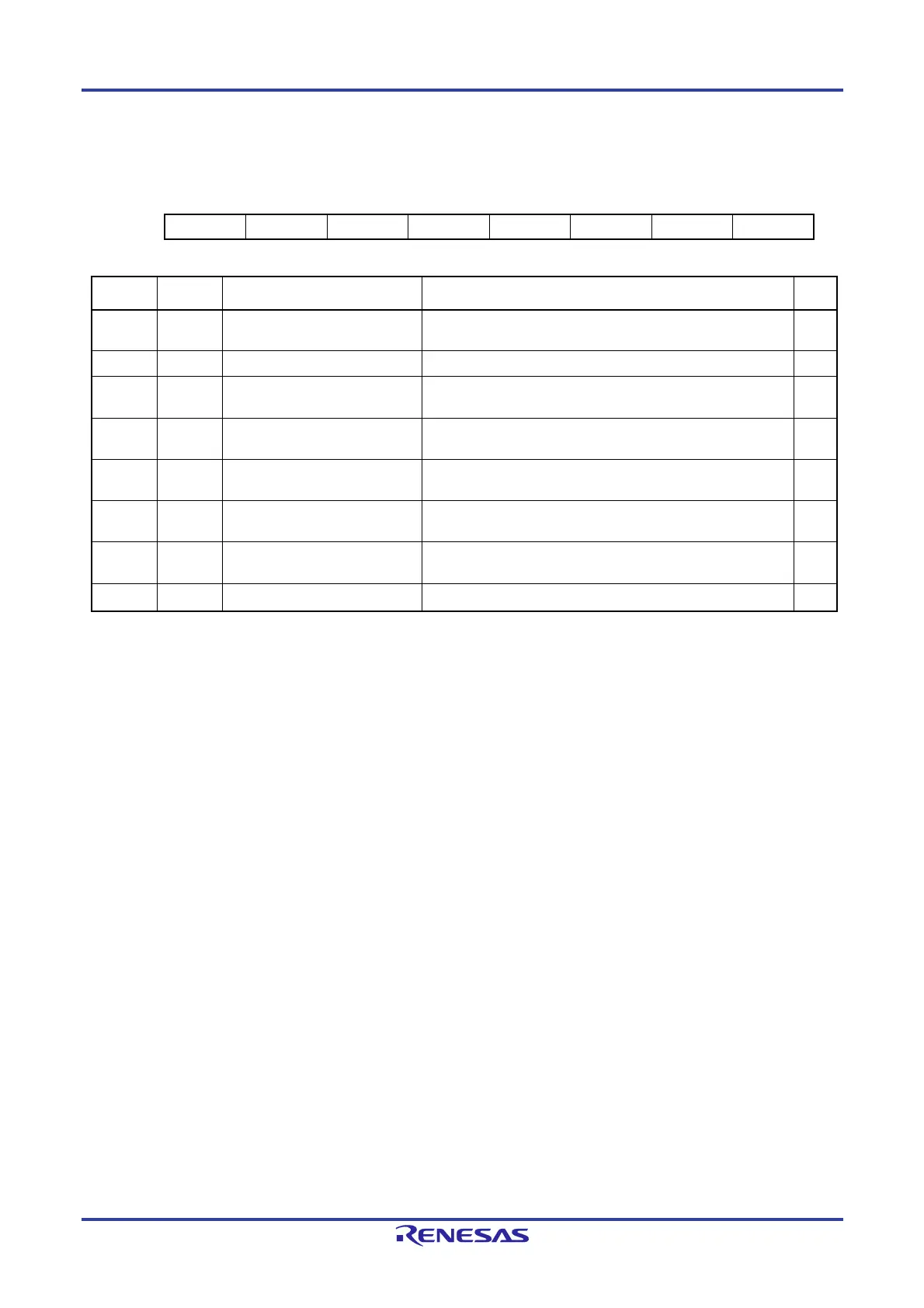

(17) LIN/UART Error Status Register (LESTn)

Address: F06D3H

7 6 5 4 3 2 1 0

— UPER IDMT EXBT FER OER — BER

Value after reset:

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Function R/W

0 BER Bit Error Flag 0: Bit error has not been detected.

1: Bit error has been detected.

R/W

1 — Reserved This bit is always read as 0. The write value should always be 0. R/W

2 OER Overrun Error Flag 0: Overrun error has not been detected.

1: Overrun error has been detected.

R/W

3 FER Framing Error Flag 0: Framing error has not been detected.

1: Framing error has been detected.

R/W

4 EXBT Expansion Bit Detection Flag 0: Expansion bit has not been detected.

1: Expansion bit has been detected.

R/W

5 IDMT ID match flag 0: Received data does not agree with the ID value.

1: Received data agrees with the ID value.

R/W

6 UPER Parity Error Flag 0: Parity error has not been detected.

1: Parity error has been detected.

R/W

7 — Reserved This bit is always read as 0. The write value should always be 0. R/W

The LESTn register is automatically cleared to 00H upon transition to LIN reset mode.

In LIN reset mode, writing to this register is disabled. In LIN reset mode, the register retains 00H.

To clear the specific bits in the register, write 0 to the bits to be cleared and write 1 to the other bits by using an 8-bit data

transfer instruction.

BER flag (bit error flag)

Only 0 can be written to the BER flag; when 1 is written, the bit retains the value that has been retained before 1 is written.

The BER flag is set to 1 upon bit error detection if the BERE bit in the LEDEn register is 1 (bit error detection is enabled). To

clear the bit to 0, write 0 to the bit.

OER flag (overrun error flag)

Only 0 can be written to the OER flag; when 1 is written, the bit retains the value that has been retained before 1 is written.

The OER flag is set to 1 upon overrun error detection if the OERE bit in the LEDEn register is 1 (overrun error detection is

enabled). To clear the bit to 0, write 0 to the bit.

FER flag (framing error flag)

Only 0 can be written to the FER flag; when 1 is written, the bit retains the value that has been retained before 1 is written.

The FER flag is set to 1 upon framing error detection if the FERE bit in the LEDEn register is 1 (framing error detection is

enabled).

In SNOOZE mode, the following conditions should also be satisfied to set this flag to 1.

The UWC bit in the LUSCn register is 1 (start of reception from STOP mode is enabled).

The USEC bit in the LUSCn register is 0 (error detection interrupt generation is enabled).

To clear the bit to 0, write 0 to the bit.

Loading...

Loading...