RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1231

Dec 10, 2015

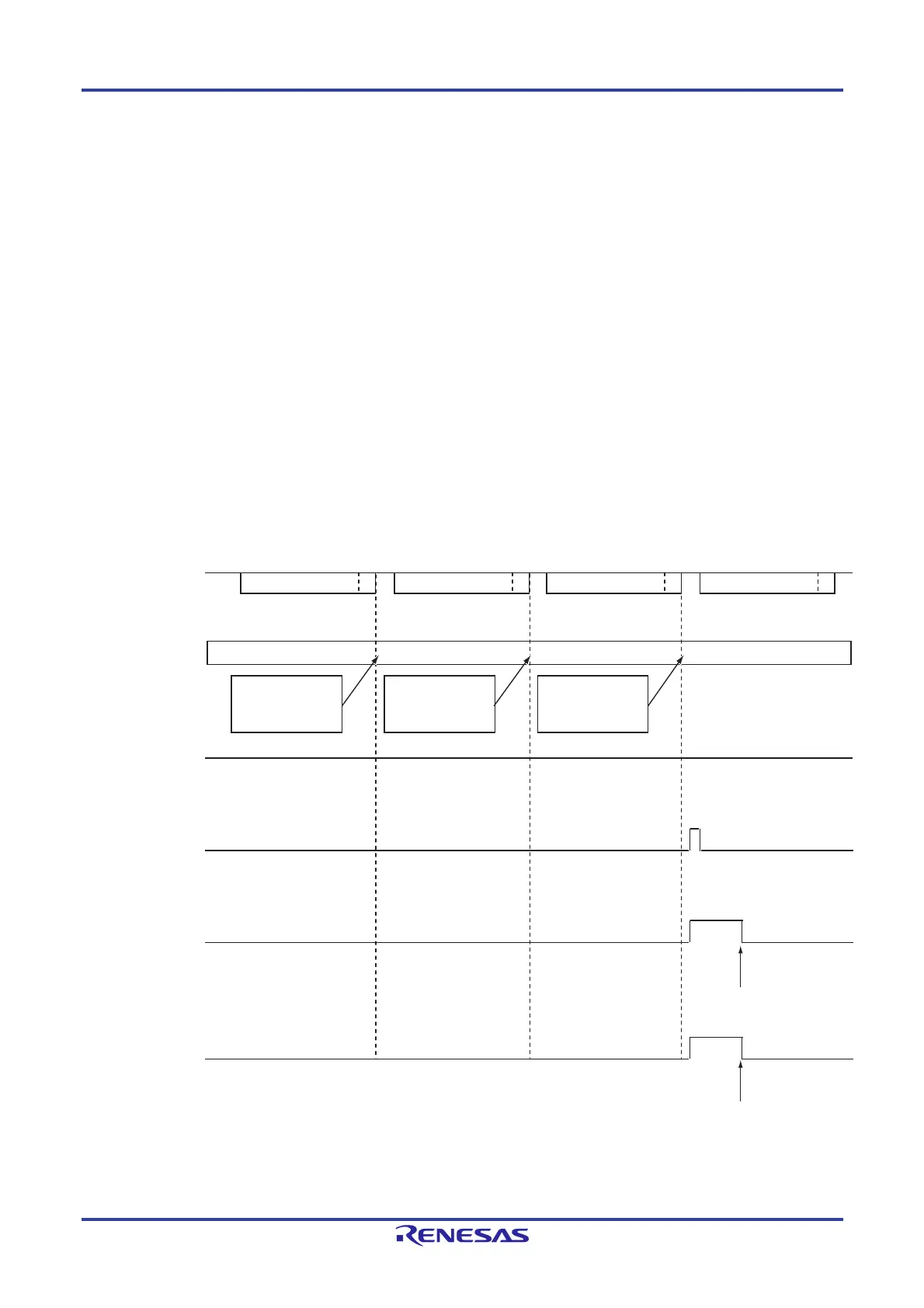

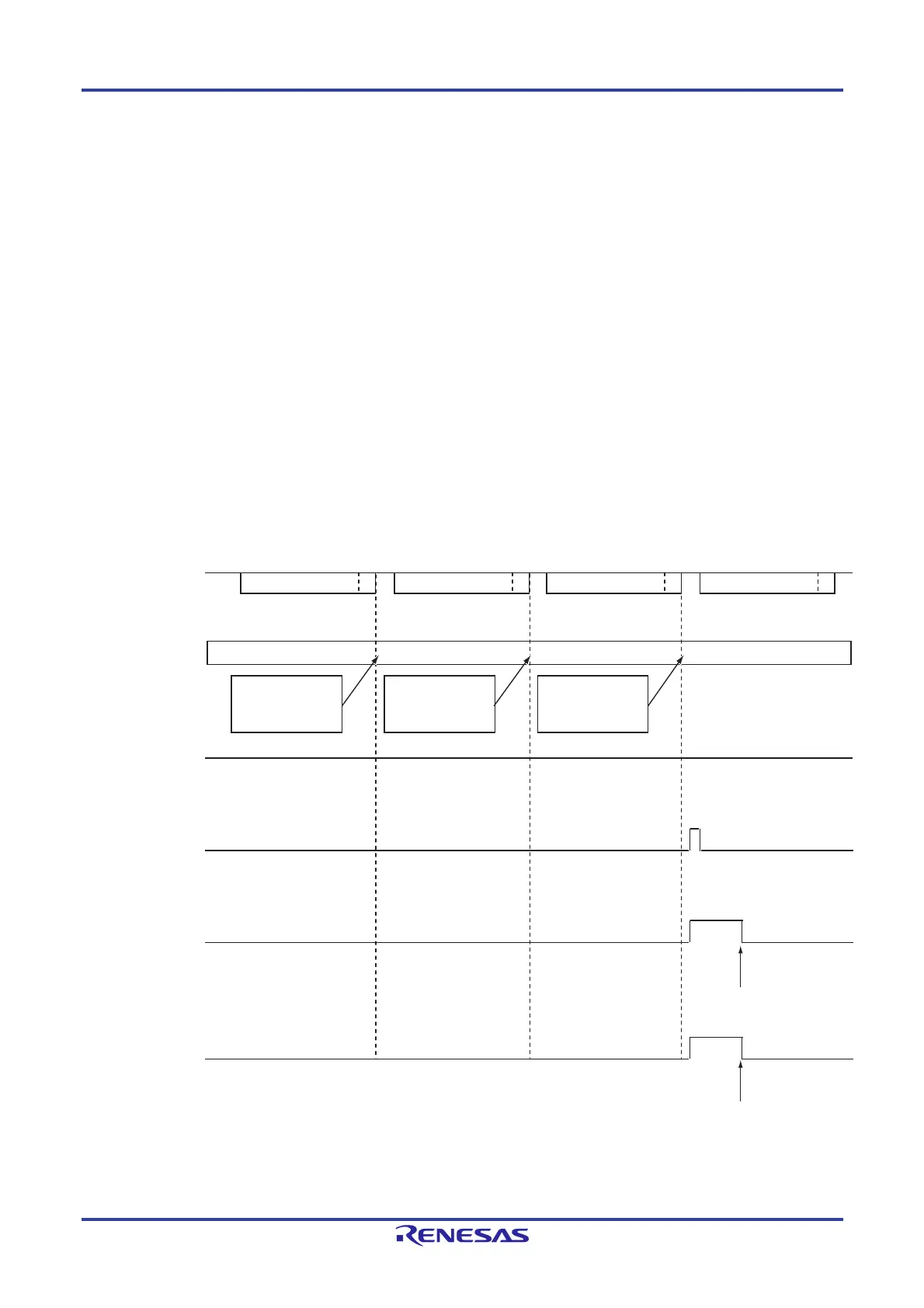

(d) Expansion Bit Reception (with Data Comparison)

The LIN/UART module (in UART mode) compares the 8-bit received data excluding the expansion bits with the

preset LIDBn register value if the level that was set in the expansion bit detection level select bit (UEBDL) is

detected when the expansion bit enable bit (UEBE) in UART option register 1 (LUORn1) is 1, the expansion bit

comparison disable bit (UECD) is 0, and the expansion bit/data comparison enable bit (UEBDCE) is 1. If the

compared two values agree, the following operations are executed.

A LINn reception status interrupt is generated (n = 0 or 1).

The expansion bit detection flag (EXBT) is set.

The ID match flag (IDMT) is set.

The received data is stored in the UART reception data register (LURDRn).

Even if the compared two values agree, a successful LINn reception interrupt is not generated.

If the compared two values do not agree, neither successful LINn reception interrupt nor LINn reception status

interrupt is generated, thus not setting the EXBT or IDMT flag to 1. Here, the received data is not stored in the

UART reception data register (LURDRn).

When changing the UEBDCE bit to 0, complete it before the next data is completely received.

Figure 17-30 shows an example when the expansion bit detection level select bit (UEBDL) is set to 0.

Figure 17-30. Expansion Bit Reception Example (with Data Comparison) (LSB First, UEBDL = 0)

Caution If a reception error (parity error, framing error, or overrun error) occurs, a LINn reception status

interrupt is generated, and the error flag is updated. In the case of an overrun error with matching of

the compare result, EXBT and IDMT flags are also set to 1.

data0 data01 data1 data2001

078

078

078

078

data1

Expansion bit not

agree and data

not compared

Expansion bit

agree and data

not agree

Expansion bit

agree and data

agree

Cleared

Cleared

LRXDn

LIDBn register

INTLINnRVC

INTLINnSTA

IDMT bit

in LESTn register

EXBT bit

in LESTn register

<R>

Loading...

Loading...