DocID024597 Rev 5 1045/1830

RM0351 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1052

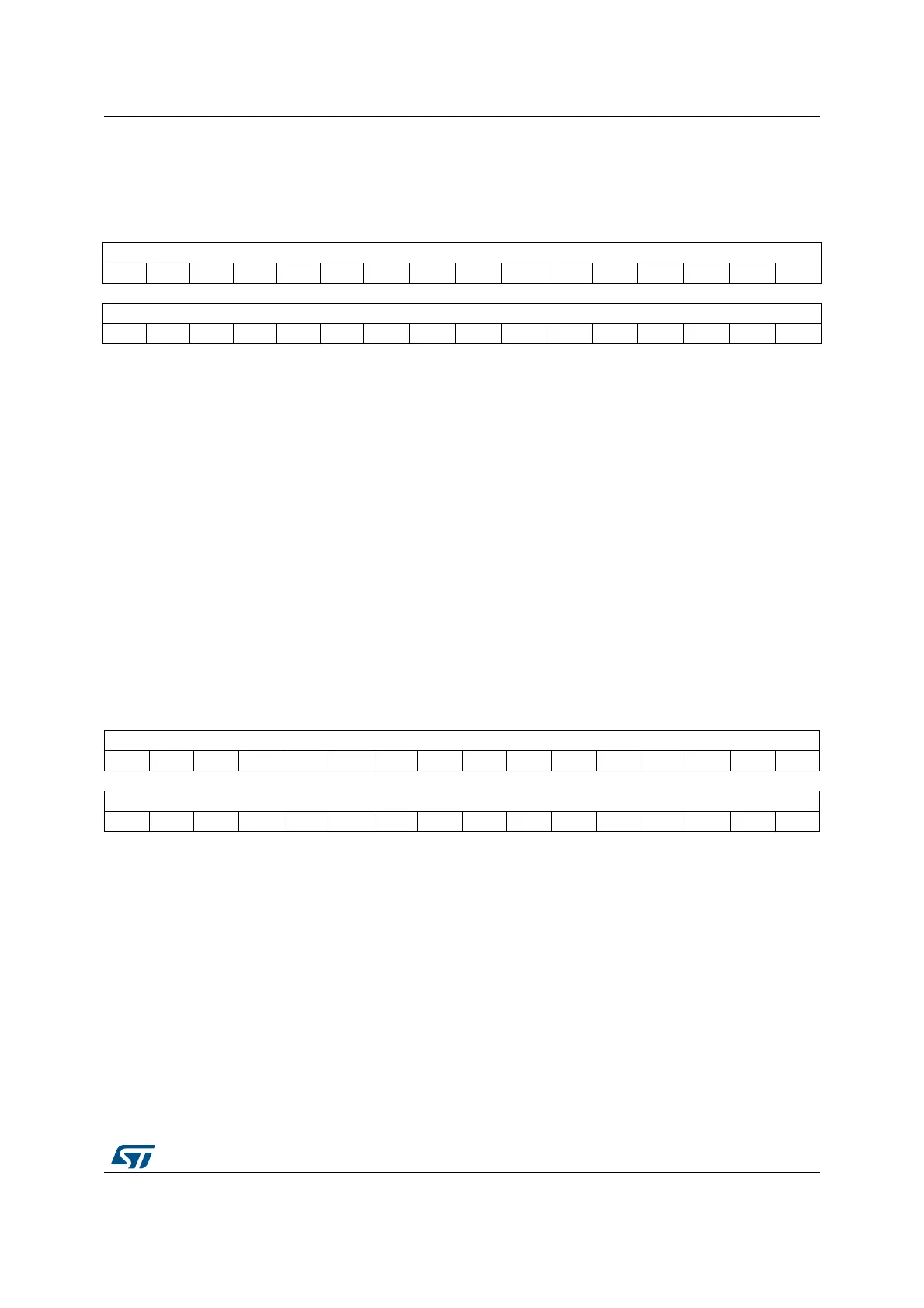

31.4.13 TIMx capture/compare register 1 (TIMx_CCR1)

Address offset: 0x34

Reset value: 0x0000

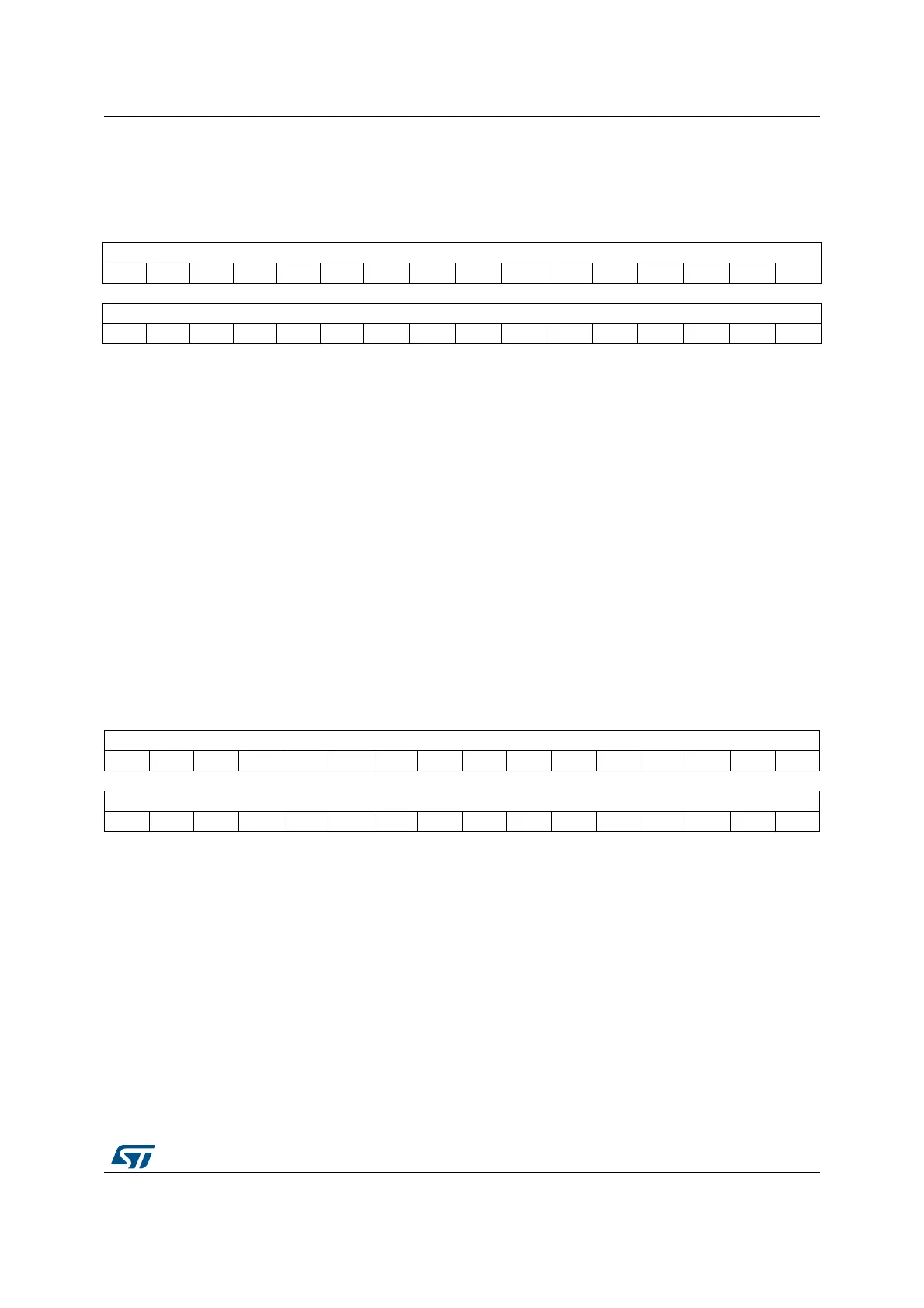

31.4.14 TIMx capture/compare register 2 (TIMx_CCR2)

Address offset: 0x38

Reset value: 0x00000000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CCR1[31:16] (depending on timers)

rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r

1514131211109876543210

CCR1[15:0]

rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r

Bits 31:16 CCR1[31:16]: High Capture/Compare 1 value (on TIM2 and TIM5)

Bits 15:0 CCR1[15:0]: Low Capture/Compare 1 value

If channel CC1 is configured as output:

CCR1 is the value to be loaded in the actual capture/compare 1 register (preload value).

It is loaded permanently if the preload feature is not selected in the TIMx_CCMR1 register

(bit OC1PE). Else the preload value is copied in the active capture/compare 1 register when

an update event occurs.

The active capture/compare register contains the value to be compared to the counter

TIMx_CNT and signaled on OC1 output.

If channel CC1is configured as input:

CCR1 is the counter value transferred by the last input capture 1 event (IC1). The

TIMx_CCR1 register is read-only and cannot be programmed.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CCR2[31:16] (depending on timers)

rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r

1514131211109876543210

CCR2[15:0]

rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r rw/r

Bits 31:16 CCR2[31:16]: High Capture/Compare 2 value (on TIM2 and TIM5)

Bits 15:0 CCR2[15:0]: Low Capture/Compare 2 value

If channel CC2 is configured as output:

CCR2 is the value to be loaded in the actual capture/compare 2 register (preload value).

It is loaded permanently if the preload feature is not selected in the TIMx_CCMR1 register

(bit OC2PE). Else the preload value is copied in the active capture/compare 2 register when

an update event occurs.

The active capture/compare register contains the value to be compared to the counter

TIMx_CNT and signalled on OC2 output.

If channel CC2 is configured as input:

CCR2 is the counter value transferred by the last input capture 2 event (IC2). The

TIMx_CCR2 register is read-only and cannot be programmed.

Loading...

Loading...