USB on-the-go full-speed (OTG_FS) RM0351

1700/1830 DocID024597 Rev 5

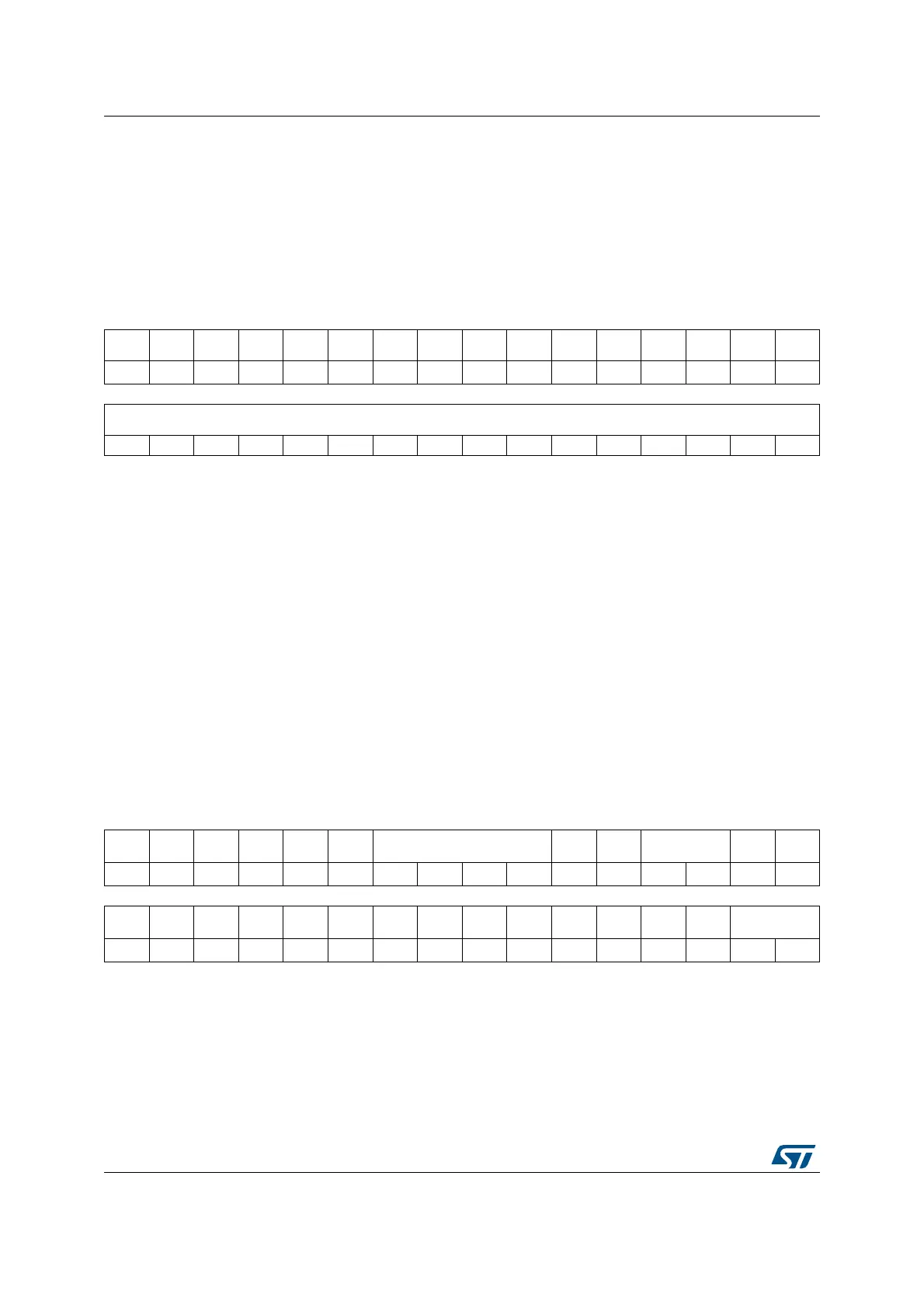

47.15.41 OTG device IN endpoint FIFO empty interrupt mask register

(OTG_DIEPEMPMSK)

Address offset: 0x834

Reset value: 0x0000 0000

This register is used to control the IN endpoint FIFO empty interrupt generation

(TXFE_OTG_DIEPINTx).

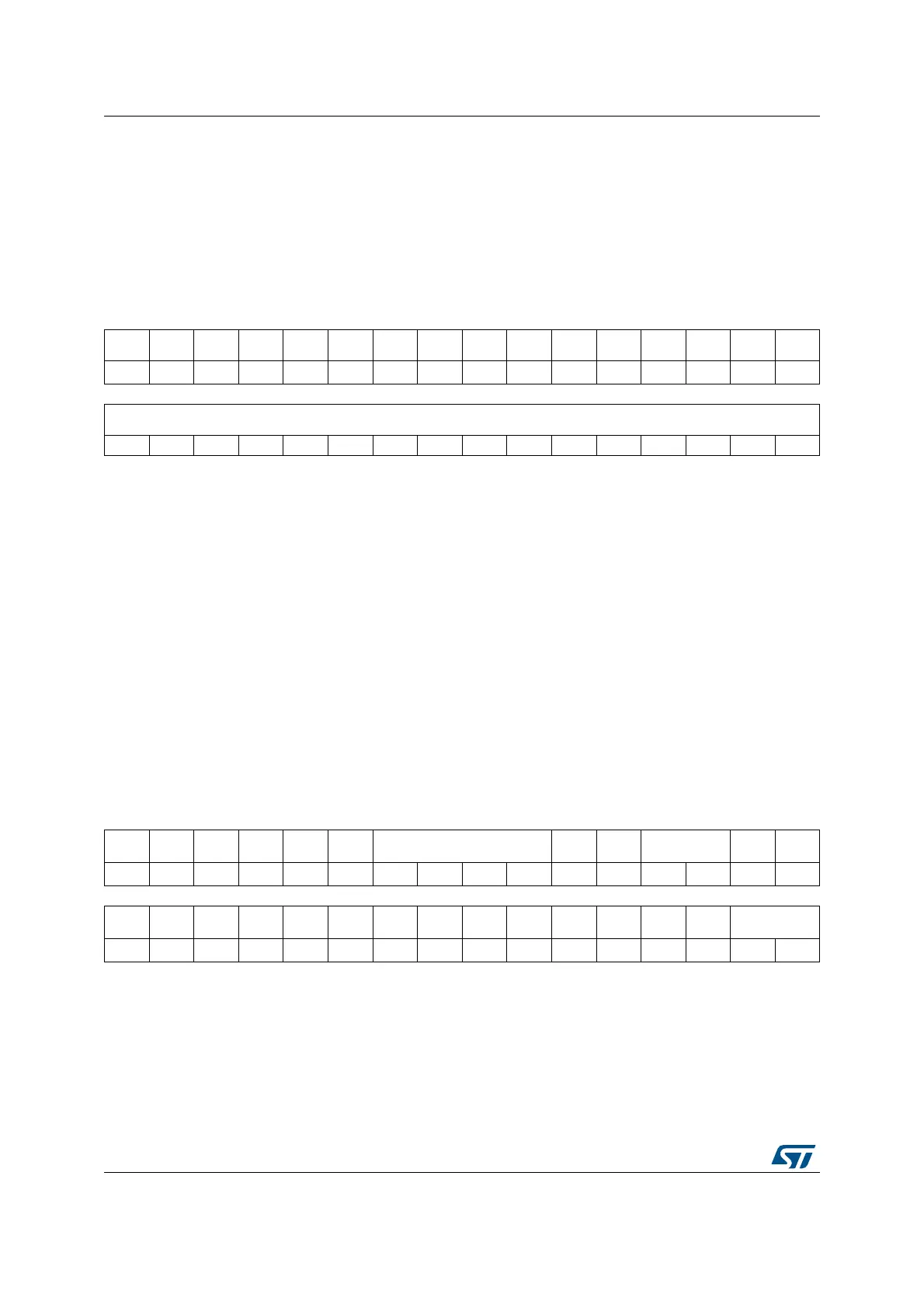

47.15.42 OTG device control IN endpoint 0 control register

(OTG_DIEPCTL0)

Address offset: 0x900

Reset value: 0x0000 0000

This section describes the OTG_DIEPCTL0 register for USB_OTG FS. Nonzero control

endpoints use registers for endpoints 1–3.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

INEPTXFEM

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 INEPTXFEM: IN EP Tx FIFO empty interrupt mask bits

These bits act as mask bits for OTG_DIEPINTx.

TXFE interrupt one bit per IN endpoint:

Bit 0 for IN endpoint 0, bit 3 for IN endpoint 3

0: Masked interrupt

1: Unmasked interrupt

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EPENA EPDIS Res. Res. SNAK CNAK TXFNUM STALL Res. EPTYP

NAK

STS

Res.

rs rs w w rw rw rw rw rs r r r

1514131211109876543210

USBA

EP

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. MPSIZ

r rw rw

Loading...

Loading...