Reset and clock control (RCC) RM0351

238/1830 DocID024597 Rev 5

6.4.11 AHB2 peripheral reset register (RCC_AHB2RSTR)

Address offset: 0x2C

Reset value: 0x00000 0000

Access: no wait state, word, half-word and byte access

Bit 8 FLASHRST: Flash memory interface reset

Set and cleared by software. This bit can be activated only when the Flash memory is in

power down mode.

0: No effect

1: Reset Flash memory interface

Bits 7:2 Reserved, must be kept at reset value.

Bit 1 DMA2RST: DMA2 reset

Set and cleared by software.

0: No effect

1: Reset DMA2

Bit 0 DMA1RST: DMA1 reset

Set and cleared by software.

0: No effect

1: Reset DMA1

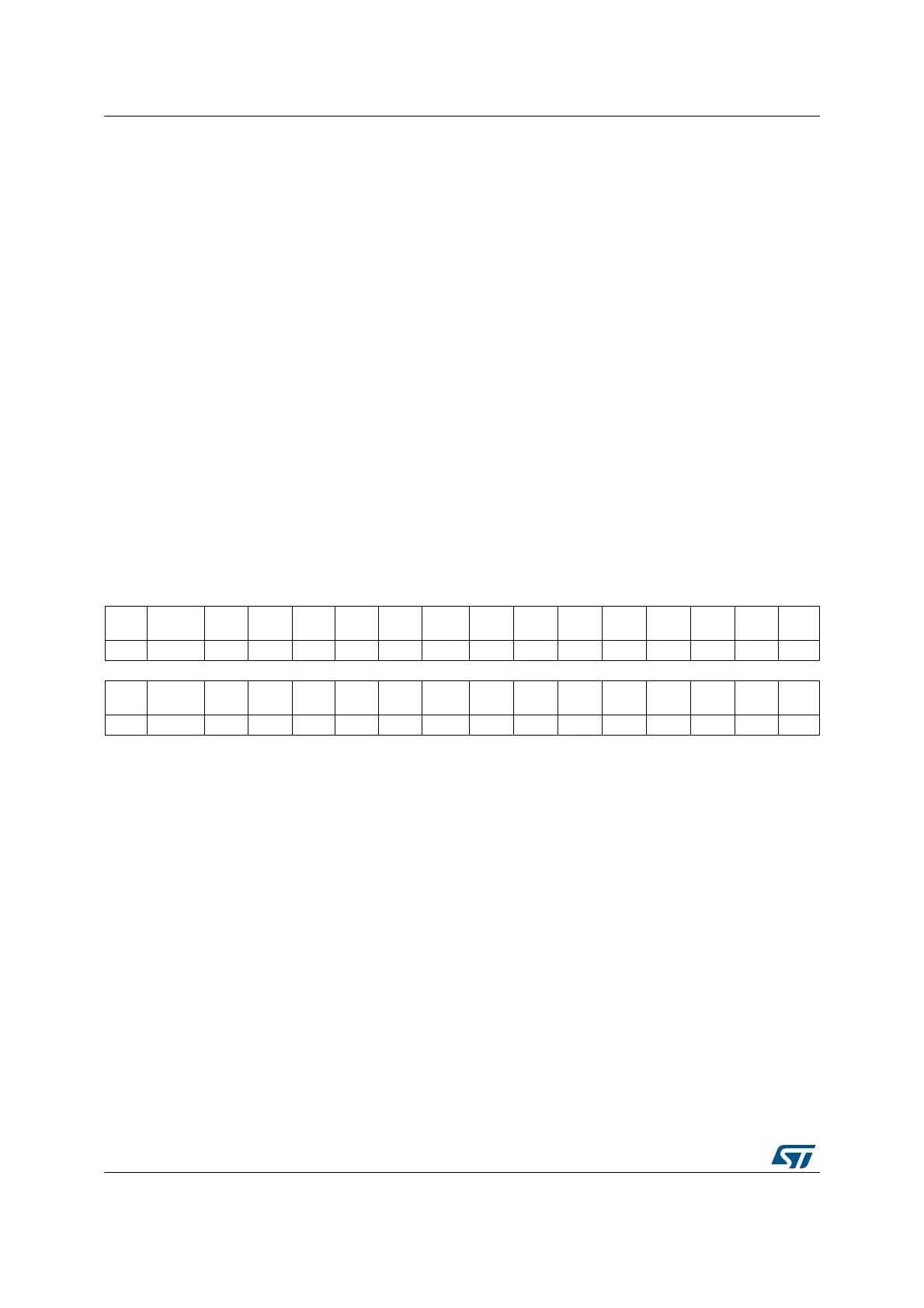

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

RNG

RST

HASH

RST

AES

RST

rw rw rw

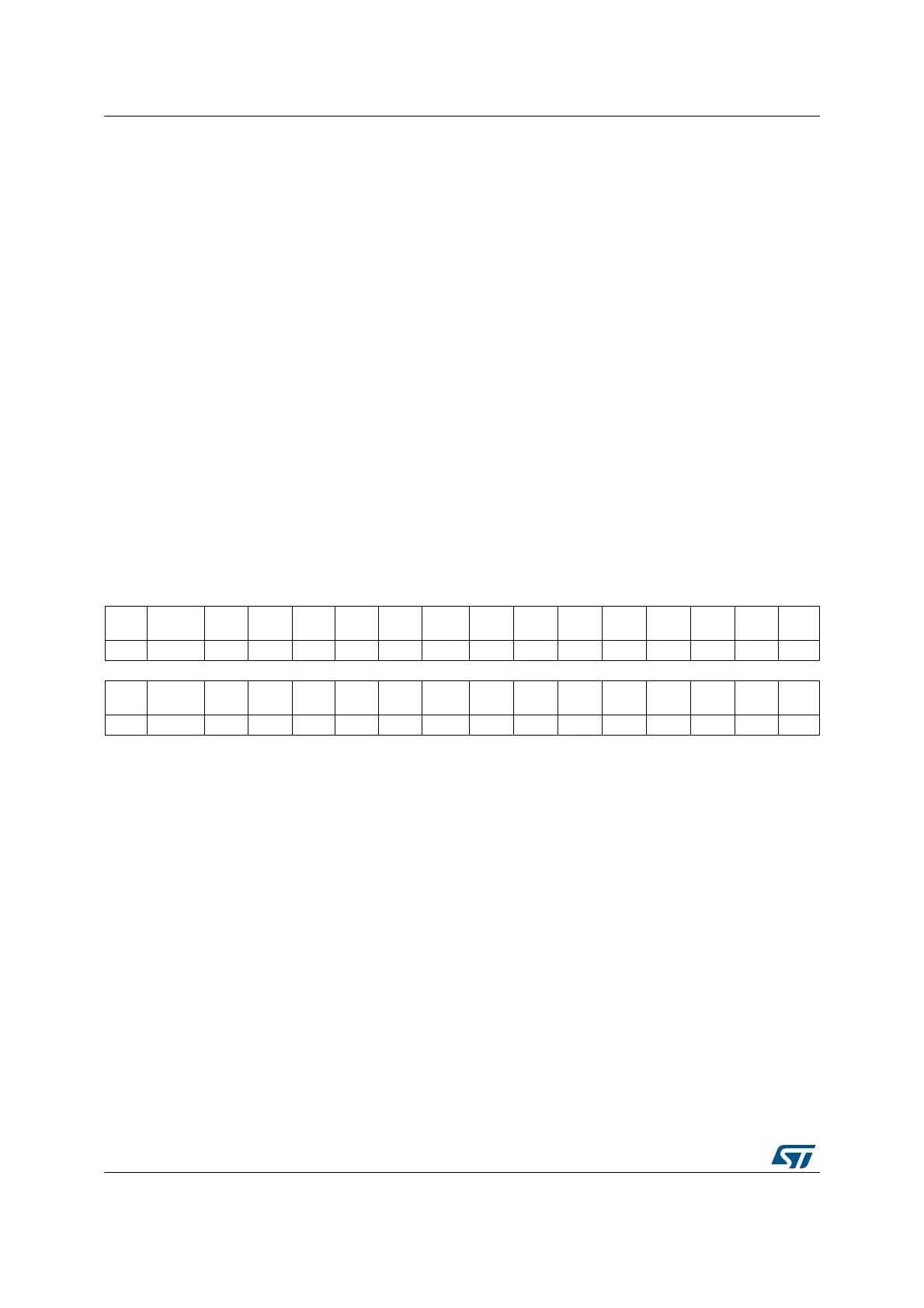

15141312111098 76543210

Res. DCMIRST

ADC

RST

OTGFS

RST

Res. Res. Res.

GPIOIR

ST

GPIOH

RST

GPIOG

RST

GPIOF

RST

GPIOE

RST

GPIOD

RST

GPIOC

RST

GPIOB

RST

GPIOA

RST

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 RNGRST: Random number generator reset

Set and cleared by software.

0: No effect

1: Reset RNG

Bit 17 HASHRST: Hash reset (This bit is reserved for STM32L475xx/476xx/486xx devices)

Set and cleared by software.

0: No effect

1: Reset HASH

Bit 16 AESRST: AES hardware accelerator reset

Set and cleared by software.

0: No effect

1: Reset AES

Bit 15 Reserved, must be kept at reset value.

Loading...

Loading...