DocID024597 Rev 5 383/1830

RM0351 Chrom-Art Accelerator™ controller (DMA2D)

391

12.5.15 DMA2D output color register (DMA2D_OCOLR)

Address offset: 0x0038

Reset value: 0x0000 0000

Bits 31:22 Reserved, must be kept at reset value

Bit 21 RBS: Red Blue Swap

This bit allows to swap the R & B to support BGR or ABGR color formats. Once the

transfer has started, this bit is read-only.

0: Regular mode (RGB or ARGB)

1: Swap mode (BGR or ABGR)

Bit 20 AI: Alpha Inverted

This bit inverts the alpha value. Once the transfer has started, this bit is read-only.

0: Regular alpha

1: Inverted alpha

Bits 19:3 Reserved, must be kept at reset value

Bits 2:0 CM[2: 0]: Color mode

These bits define the color format of the output image. These bits can only be written

when data transfers are disabled. Once the transfer has started, they are read-only.

000: ARGB8888

001: RGB888

010: RGB565

011: ARGB1555

100: ARGB4444

others: meaningless

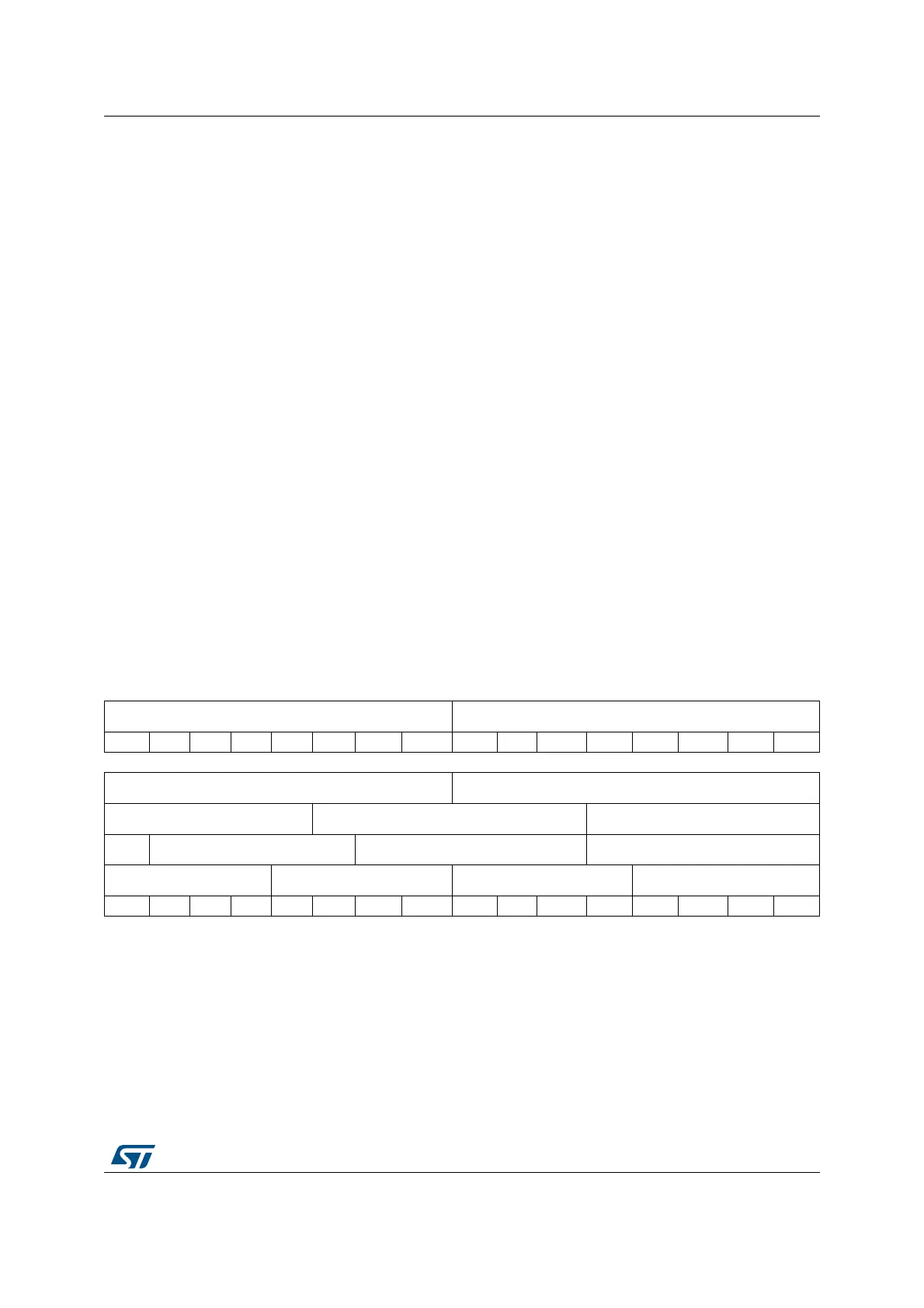

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ALPHA[7:0] RED[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

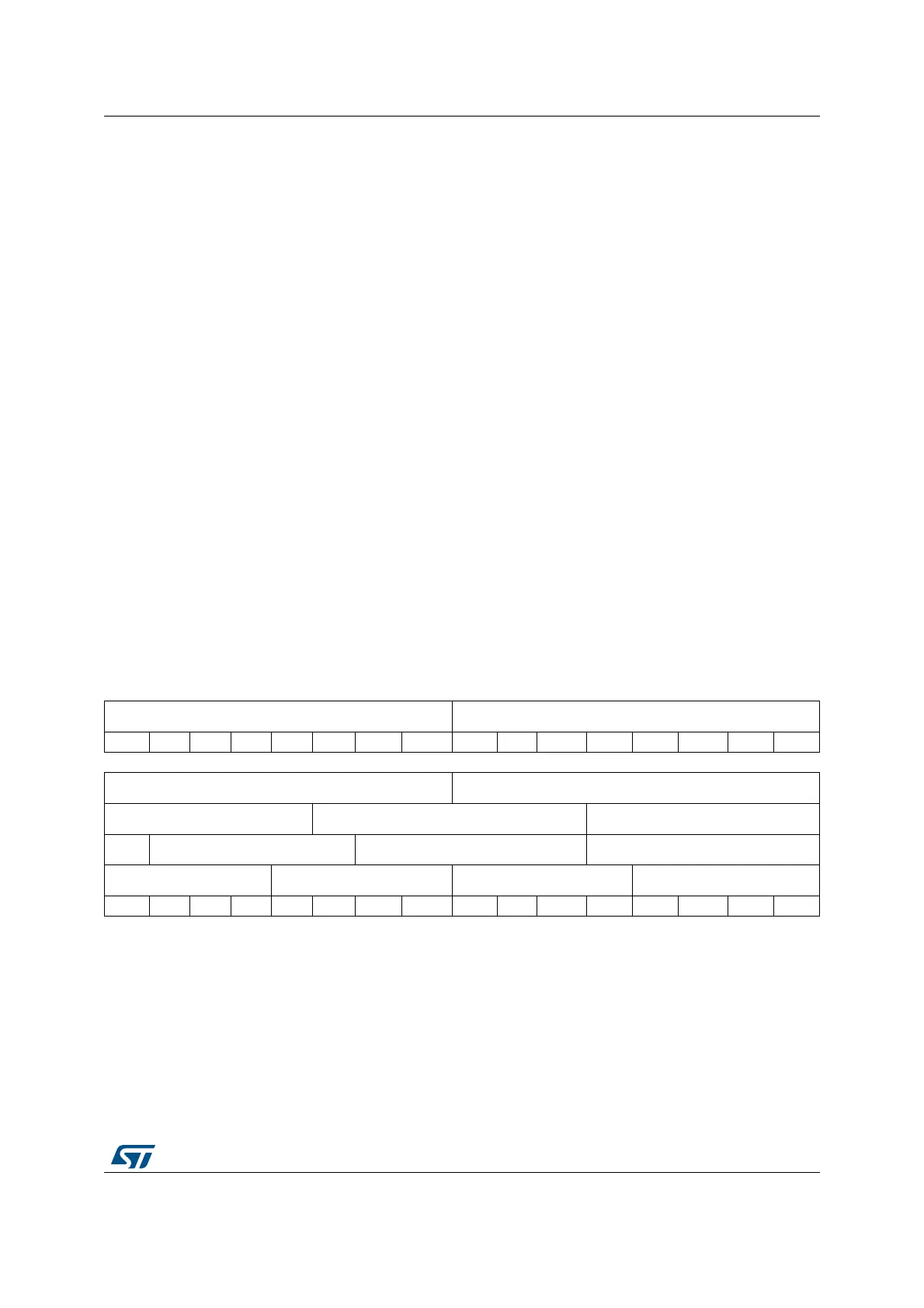

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

GREEN[7:0] BLUE[7:0]

RED[4:0] GREEN[5:0] BLUE[4:0]

A RED[4:0] GREEN[4:0] BLUE[4:0]

ALPHA[3:0] RED[3:0] GREEN[3:0] BLUE[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 ALPHA[7: 0]: Alpha Channel Value

These bits define the alpha channel of the output color. These bits can only be written

when data transfers are disabled. Once the transfer has started, they are read-only.

Loading...

Loading...