Digital-to-analog converter (DAC) RM0351

616/1830 DocID024597 Rev 5

19.3 DAC functional description

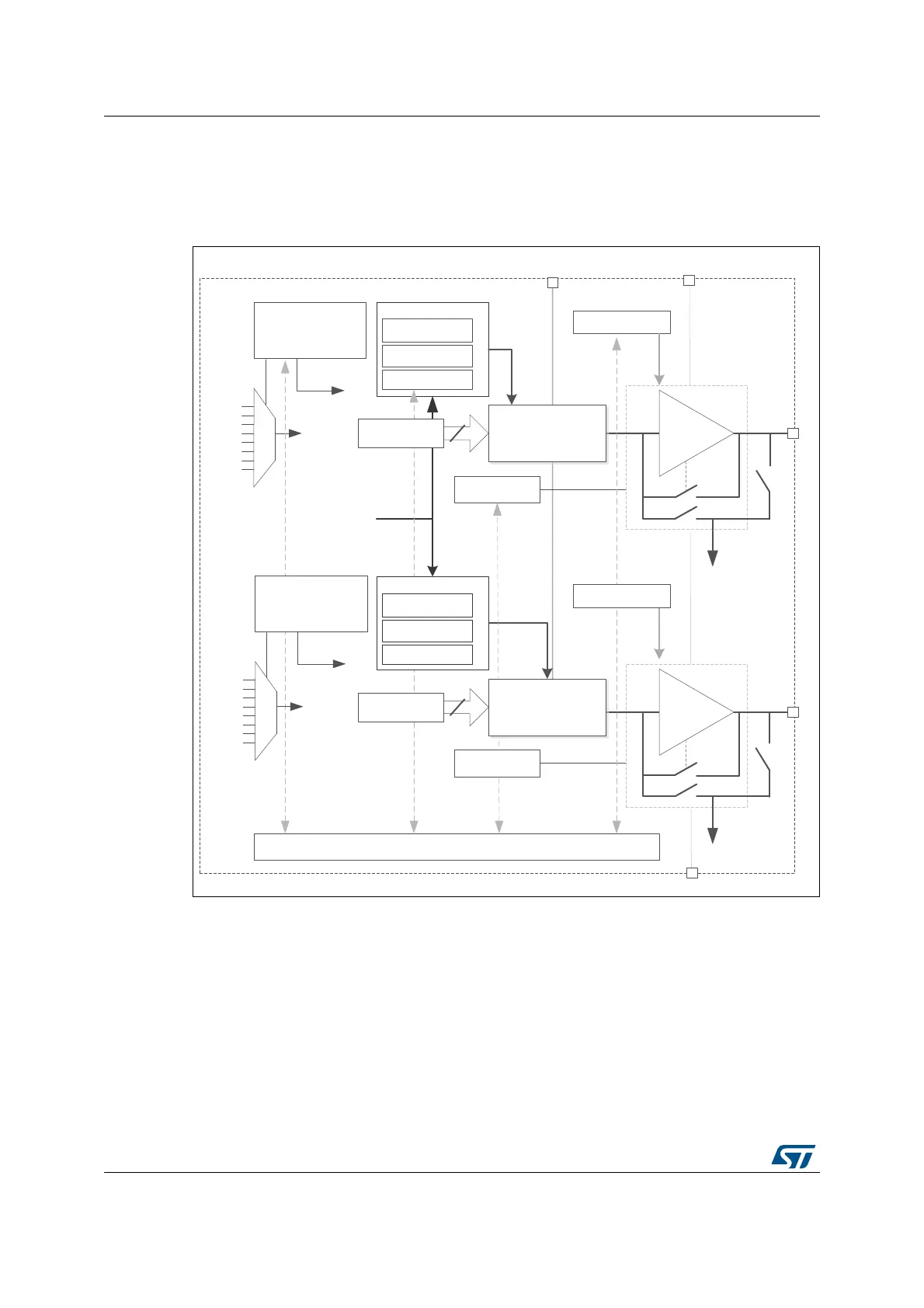

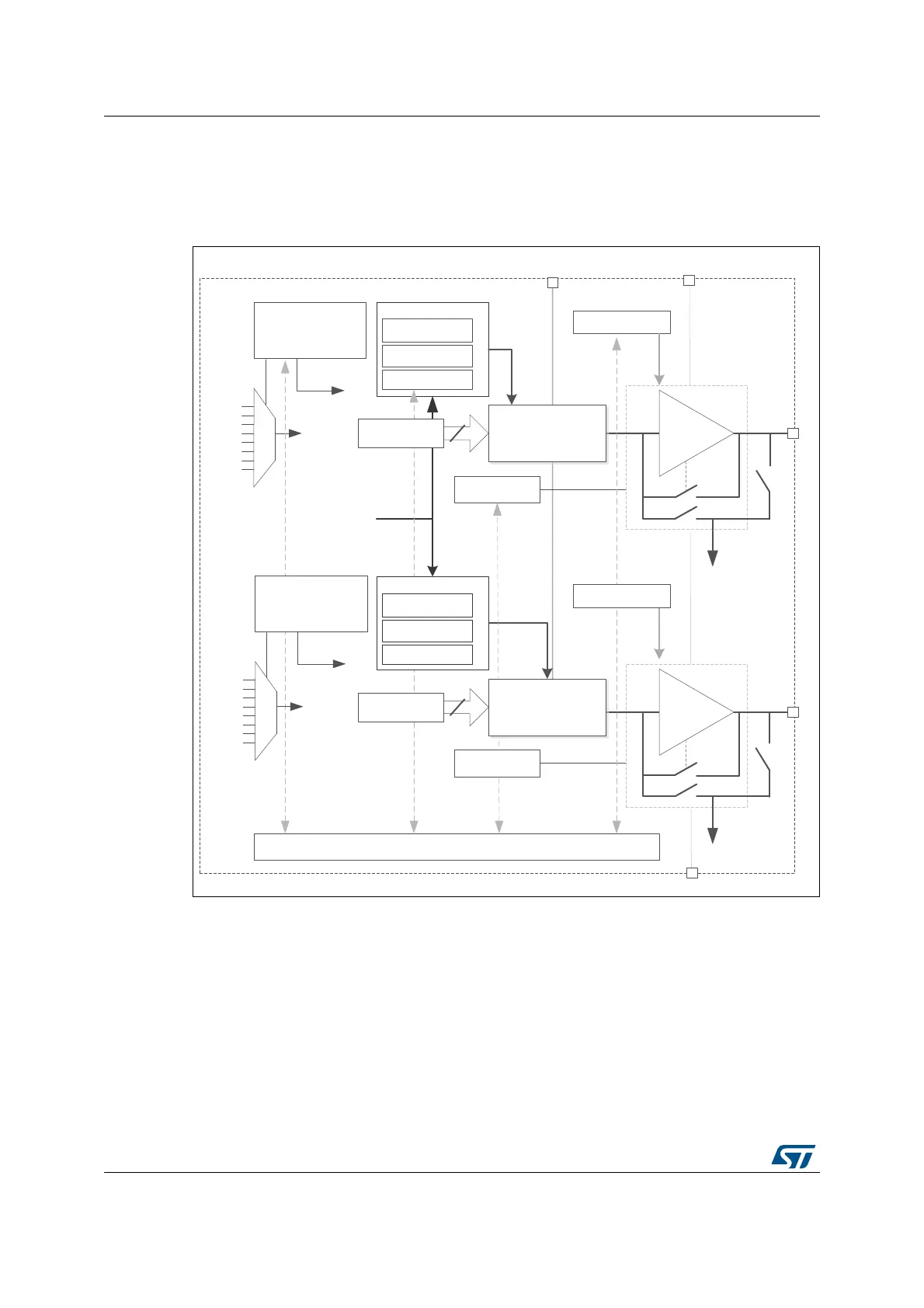

19.3.1 DAC block diagram

Figure 137. DAC channel block diagram

1. The output mode controller switches between the normal mode in buffer/unbuffered configuration and the

Sample and Hold mode.

The DAC includes:

• Up to two output channels

• The DAC_OUTx can be disconnected from output pin and used as ordinary GPIO

• The DAC_OUTx can used internal pin connection to on-chip peripherals such as

comparators and OPAMPs.

• DAC output channel buffered or non buffered

• Sample and hold block and registers using LSI clock source and operational in Stop

mode for static conversion

06Y9

sZ&н

s

KŶͲĐŚŝƉ

WĞƌŝƉŚĞƌĂůƐ

džͺKhdϭ

ƵĨĨĞƌϭ

ĐŽŶǀĞƌƚĞƌϭ

džͺKhdϮ

ƵĨĨĞƌϮ

s^^

ϭϮͲďŝƚ

DKϭďŝƚƐ

d^DW>ϭ

d,K>ϭ

dZ&Z^,ϭ

^ĂŵƉůĞΘ,ŽůĚZĞŐŝƐƚĞƌƐ

KdZ/DϭϱϬďŝƚƐ

ŽŶƚƌŽůƌĞŐŝƐƚĞƌƐ

ΘůŽŐŝĐŚĂŶŶĞůϭ

ϭϮͲďŝƚ

>^/ĐůŽĐŬ

d^>ϭϮϬ

ďŝƚƐ

DͺZĞƋƵĞƐƚ

d/DϲͺdZ/'

d/DϴͺdZ/'

d/DϳͺdZ/'

KŶͲĐŚŝƉ

WĞƌŝƉŚĞƌĂůƐ

d/DϱͺdZ/'

d/DϮͺdZ/'

d/DϰͺdZ/'

yd/ϵͺdZ/'

^tͺdZ/'

dZ/'

d^>ϮϮϬ

ďŝƚƐ

DͺZĞƋƵĞƐƚ

d/DϲͺdZ/'

d/DϴͺdZ/'

d/DϳͺdZ/'

d/DϱͺdZ/'

d/DϮͺdZ/'

d/DϰͺdZ/'

yd/ϵͺdZ/'

^tͺdZ/'

dZ/'

KĨĨƐĞƚĐĂůŝďƌĂƚŝŽŶ

WϭƵƐ

džͺKZϮ

ŽŶƚƌŽůƌĞŐŝƐƚĞƌƐ

ΘůŽŐŝĐŚĂŶŶĞůϮ

džͺKZϭ

^ĂŵƉůĞΘ,ŽůĚZĞŐŝƐƚĞƌƐ

d^DW>Ϯ

d,K>Ϯ

dZ&Z^,Ϯ

ĐŽŶǀĞƌƚĞƌϮ

DKϮďŝƚƐ

KdZ/DϮϱϬďŝƚƐ

KĨĨƐĞƚĐĂůŝďƌĂƚŝŽŶ

Loading...

Loading...