DocID024597 Rev 5 641/1830

RM0351 Digital-to-analog converter (DAC)

647

19.5.15 DAC calibration control register (DAC_CCR)

Address offset: 0x38

Reset value: 0x00XX 00XX

Bit 31 BWST2: DAC Channel 2 busy writing sample time flag

This bit is systematically set just after Sample & Hold mode enable and is set each time the

software writes the register DAC_SHSR2, It is cleared by hardware when the write operation of

DAC_SHSR2 is complete. (It takes about 3 LSI periods of synchronization).

0:There is no write operation of DAC_SHSR2 ongoing: DAC_SHSR2 can be written

1:There is a write operation of DAC_SHSR2 ongoing: DAC_SHSR2 cannot be written

Bit 30 CAL_FLAG2: DAC Channel 2 calibration offset status

This bit is set and cleared by hardware

0: calibration trimming value is lower than the offset correction value

1: calibration trimming value is equal or greater than the offset correction value

Bit 29 DMAUDR2: DAC channel2 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel2

1: DMA underrun error condition occurred for DAC channel2 (the currently selected trigger is

driving DAC channel2 conversion at a frequency higher than the DMA service capability rate)

Bits 28:16 Reserved, must be kept at reset value.

Bit 15 BWST1: DAC Channel 1 busy writing sample time flag

This bit is systematically set just after Sample & Hold mode enable and is set each time the

software writes the register DAC_SHSR1, It is cleared by hardware when the write operation of

DAC_SHSR1 is complete. (It takes about 3 LSI periods of synchronization).

0:There is no write operation of DAC_SHSR1 ongoing: DAC_SHSR1 can be written

1:There is a write operation of DAC_SHSR1 ongoing: DAC_SHSR1 cannot be written

Bit 14 CAL_FLAG1: DAC Channel 1 calibration offset status

This bit is set and cleared by hardware

0: calibration trimming value is lower than the offset correction value

1: calibration trimming value is equal or greater than the offset correction value

Bit 13 DMAUDR1: DAC channel1 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel1

1: DMA underrun error condition occurred for DAC channel1 (the currently selected trigger is

driving DAC channel1 conversion at a frequency higher than the DMA service capability rate)

Bits 12:0 Reserved, must be kept at reset value.

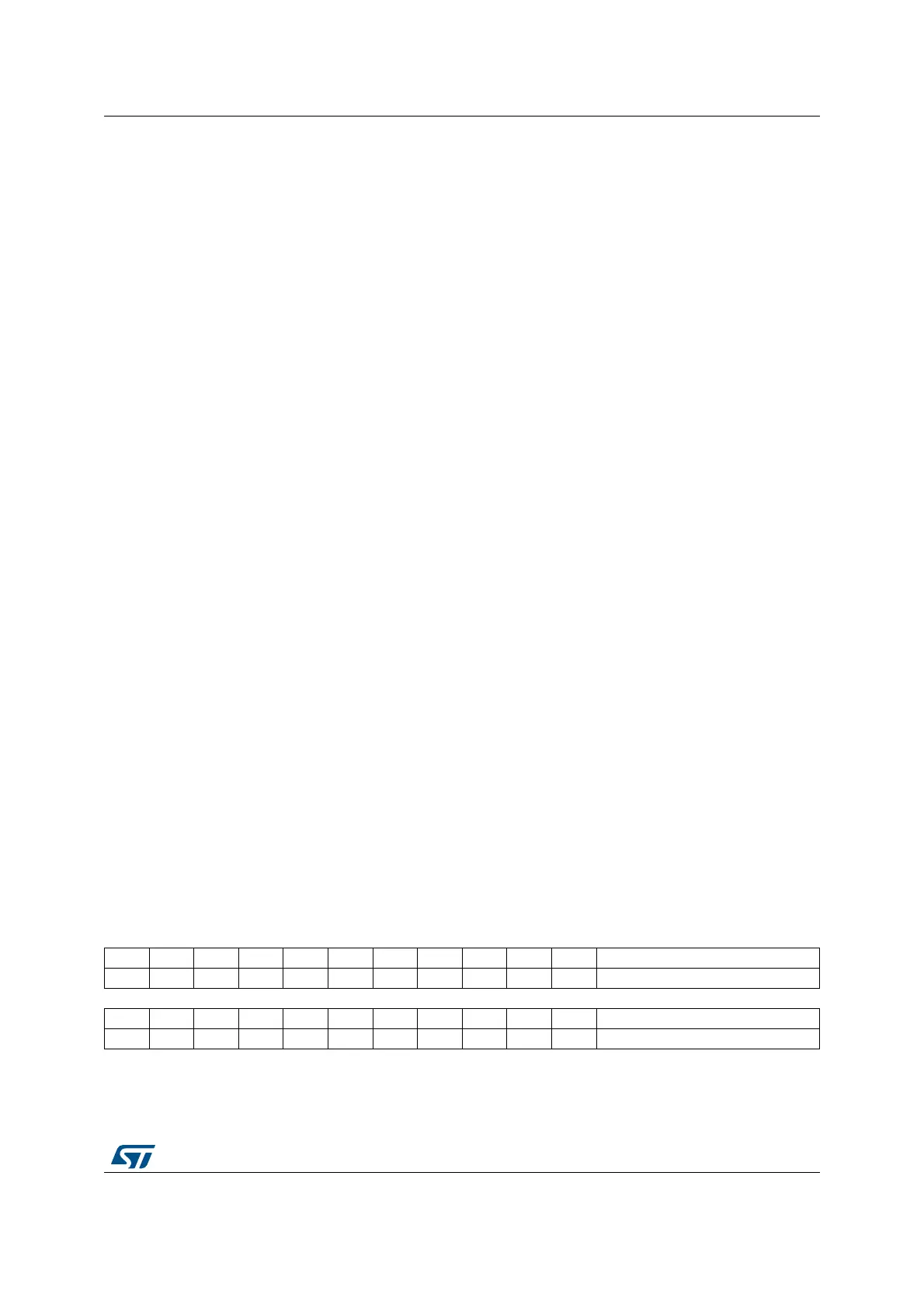

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OTRIM2[4:0]

rw

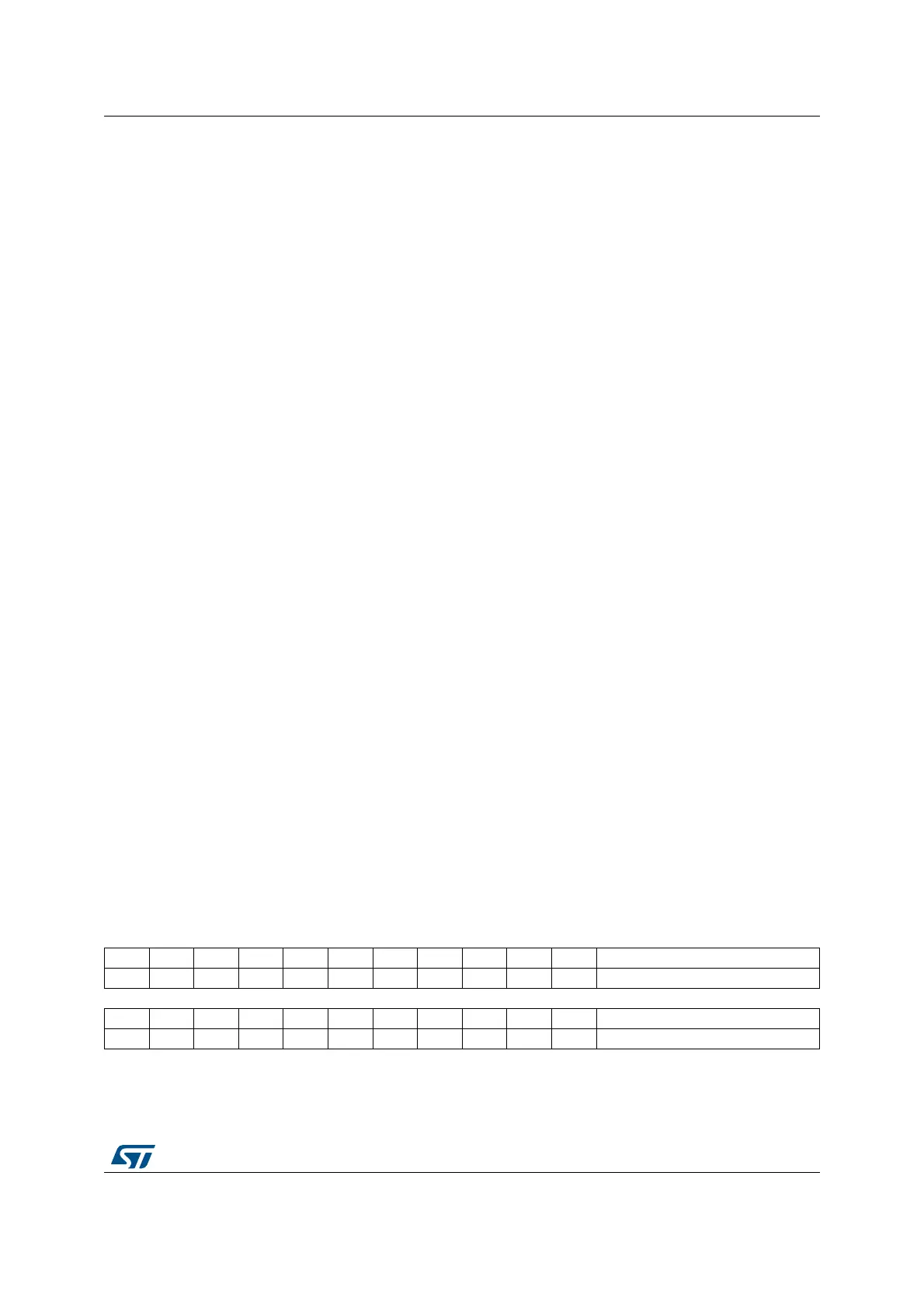

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OTRIM1[4:0]

rw

Loading...

Loading...